Setting Things Up

Under this chapter, we intend to answer the following 3 questions :

- What are we setting up?

- Why are we setting up those things?

- How are we seting up those things?

What are we setting up?

We are setting up a development toolchain, RISCV virtual environment and a no-std Rust file.

The development Toolchain

A toolchain is a group of software tools that typically get used together...a chain of tools...

In OS Development, the name toolchain usually refers to the combination of the compiler, linker, debugger and a bunch of programs that help in inspecting files. This toolchain gets used to convert source code into a format that can run on an execution environment.

An execution environment is a place where a software program can run. It provides the necessary resources, like the operating system and libraries, that the program needs to function. Examples of execution enviroments include: Bare metal, Browsers, Virtual Machines, Operating systems and Containers.

The toolchain in our case will consist of the following tools :

- The Rust Nightly Compiler with a riscv64gc-unknown-none-elf backend

- linker : Rust-lld

- Binutils

- Make

To our luck, we do not have to install all these elements seperately. There exists compact toolchains :

- LLVM Riscv toolchain

- The GNU Riscv Toolchain

- The Rust Toolchain

Why we need the toolchain

We will have two kinds of source code files in our project : Rust source files and RISCV-Assembly files. Both of these types of files need to be turned into object files. Afterwards, those object files need to get linked together into a single executable file.

We can go about this process of creating a single executable file in two ways:

Method 1

We can compile the Rust files seperately from the Assembly files.

Meaning that we will use a stand-alone assembler to assemble the RISCV assembly files and turn them into object code.

Later, we will then compile the RUST files into object code using a RUST_compiler.

Afterwords we can combine the resultant object files using a linker to form a single executable.

Method 2

We can embed the assembly code into the Rust source code.

That way, we only need one compilation, we will only need to compile the asm_embedded Rust files. This method seems more of 'plug and play'.

The disadvantage of this method is that we will always have to re-compile every file each time we change anything in any source file. But this is not really a problem. Modern compilers are Fast. Using method one will save up a few nano_seconds. A few nanoseconds is cheap price to pay.

Method 2 is a more user friendly method. Trading off negligible compile time over a user-friendliness in building and tweaking configurations is by far a very good choice.

Moreover, the rust compiler comes with its own inbuilt LLVM linker, rust-lld. That means that once we hit compile, we get the executable file output. One click, and all the build process runs inbuilt; from compiling rust files, to compiling assembly files, to creating a riscv-compliant executable file.

No more Makefiles nightmares, no more. This is very big news.

For this reason, we will use Method 2.

The Rust LLVM compiler and Targets

The Linker

references

Setting Up the Compiler

The compiler is the tool that will convert our source code to machine code that suits a specific machine target.

In our case, that specific machine target is "The RISCV CPU, bare metal".

The rust compiler gets installed as a toolchain, so it comes with a linker attached. For this reason, our compile button will do the following :

- Compile rust files

- Compile the embedded assembly files.

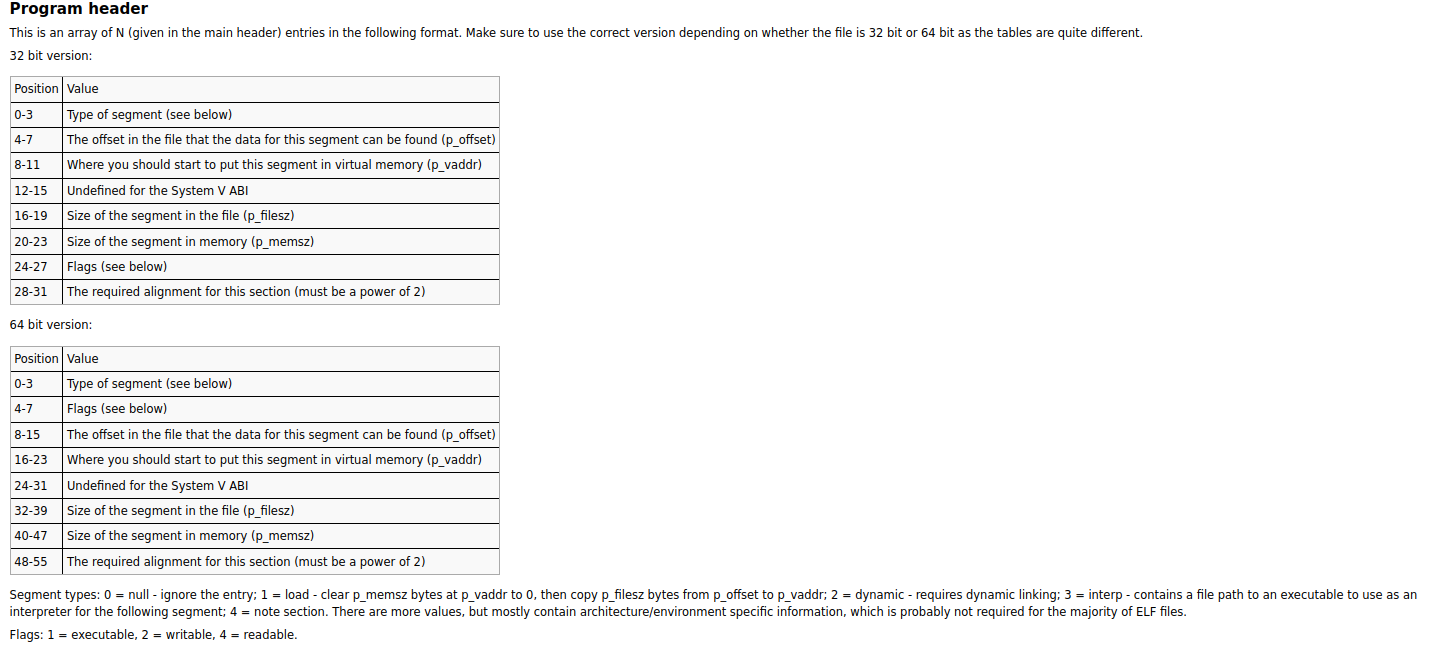

- Link all the object files and produce an executable ELF file. (linker part)

Ofcourse you an use a 3rd party linker that you prefer, you are not forced to use the attached linker. But using another linker looks like a lot of unnecessary hard work.

In the compiler world, people identify compilation targets using a standard naming convention called "Target Triple".

Initially the Target triple specified three characteristics of the machine target :

- CPU Architecture : eg x86, RISCV, ARM

- Vendor who manufactures the target : eg Apple, IBM

- The operating system running on the CPU : eg Linux, Windows, FreeBSD, None

For example you would define a target as : ARM-Apple-IoS

But the world got more complex, now we have people naming things like... i don't know... it is not 3 characteristics anymore. Sometimes you have 2 sometimes 5, 4 or 3.

So here is a 4 identifier description : - CPU architecture - Vendor - Operating System - ABI

Really, there is confusion, but hopefully you can tell what stands for what when you see a triple target with a weird number of identifiers.

Commands

To install the Stable Rust compiler, enter the following comand :

curl --proto '=https' --tlsv1.2 -sSf https://sh.rustup.rs | sh

Alternatively, you can visit this page : Rust Compiler installation Main Page

But in our project, we will use Nightly features. So you will need to install Rust Nightly :

rustup toolchain install nightly //install nightly Compiler

rustup default nightly // set nightly Compiler as the default toolchain

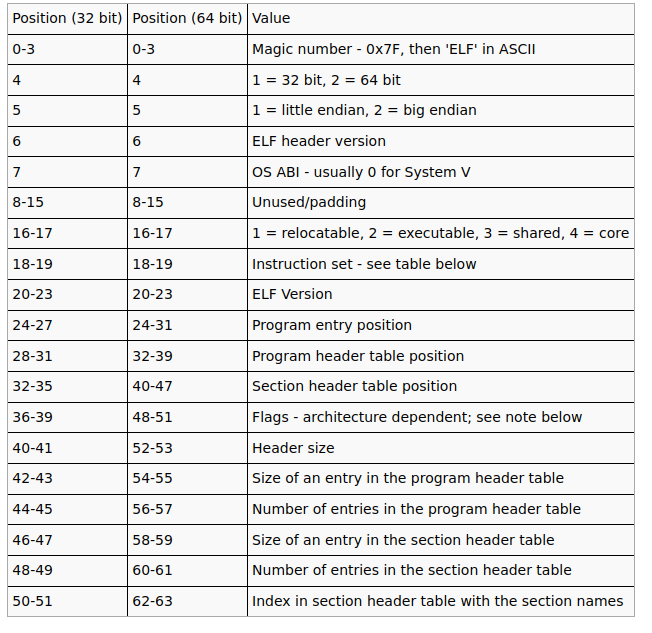

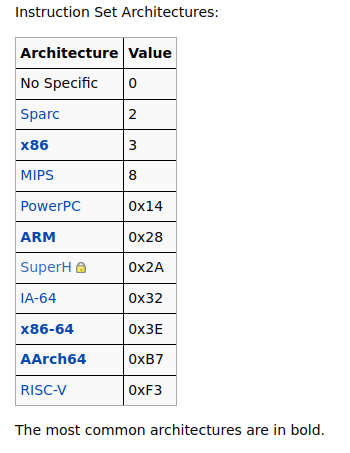

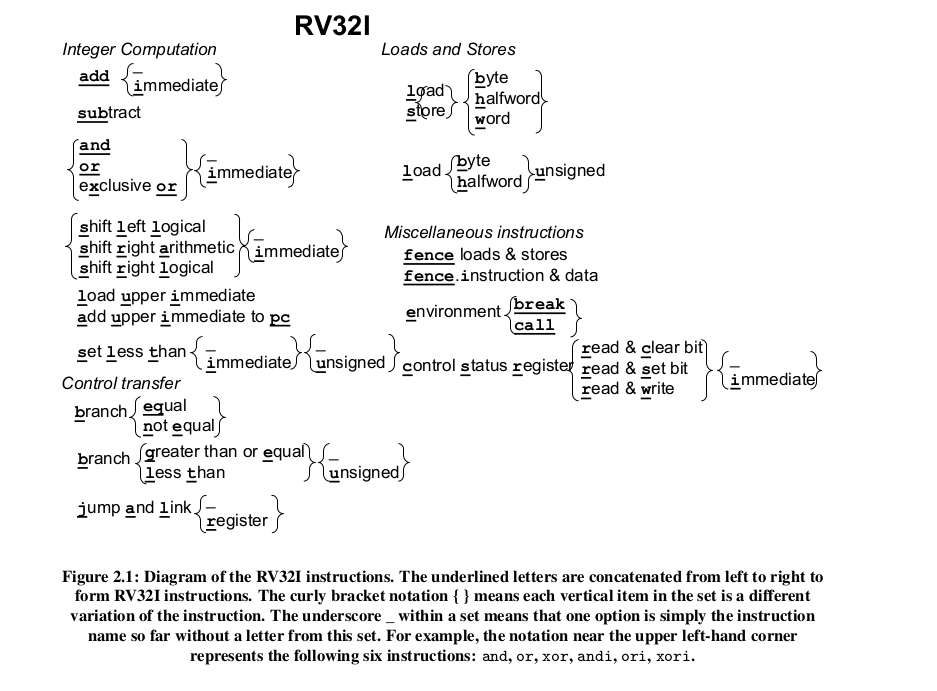

The Machine Target we are compiling for is "riscv64gc-unknown-none-elf" which means we are compiling for

- "riscv646gc - 64-bit-Riscv CPU that : supports all general instructions 'g' and supports compressed instructions 'c'

- unknown - means that the manufaturer of the CPU is unknown or that info is irrelevant

- none - means that the CPU has no operating system running on top of it

- elf - This component identifies the format of the output binary file that will be generated by the compiler. In this case, it specifies that the binary file will be in the ELF (Executable and Linkable Format) format, which is a common format used for executables and shared libraries on Unix-based systems.

To check out all the targets that the compiler can support by default, type the following comand :

rustup target list // list all supported targets

rustup target list --installed // list all installed supported targets

To install our riscv64gc-unknown-none-elf target, enter th following command ;

rustup target add riscv64gc-unknown-none-elf // install a supported target

If you come up with your own custom target, you can tweak the toolchain to support your target. Like for our case, we are going to come write an operating system. The toolchain does not know our OS, So people are not able to compile specifically for our OS. That topic is discussed here

We are done setting up the compiler!!!

Setting up the linker

References :

As earlier mentioned, the Rust compiler comes with an inbuilt linker. Each target comes with its own configured linker

So by default we do not need a linker script. But as for our case, we need a linker script.

Why?

Reason 1: The default compiler does not know the name of your entry_point function. Normally, the linker deals with rust crates that depend on the std libraries, and the entry_point of these crates is "_start"-->"start"-->"main" by default. In our case the linker has no clue. We need to tell it using a linker script.

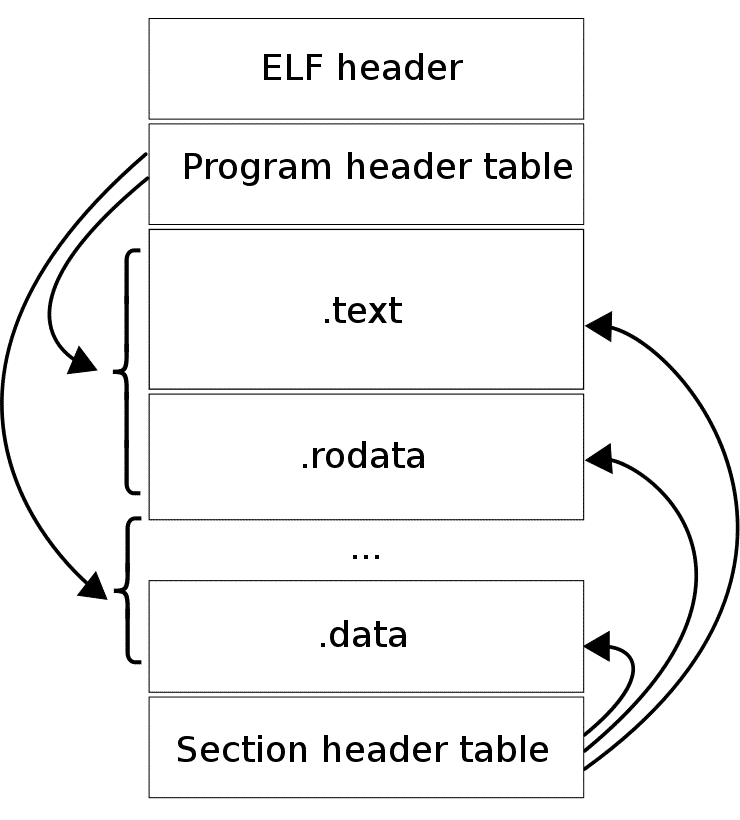

Reason 2: Here is the thing, the elf file has many sections. the global_data section, the heap, the stack, the bss, the text section...

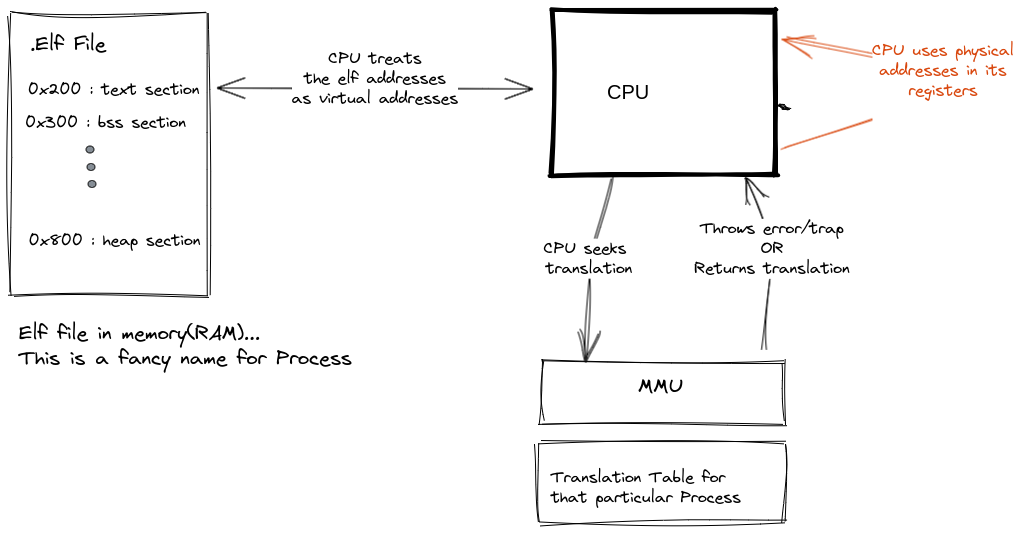

To write kernel code, you need to know the memory addresses of different elf sections.

For example....

When programming how the kernel heap will get allocated and deallocated, you will need to know the exact memory address of the heap and you will reference it in your allocating function using a pointer. Or when you want the bootloader to point to the text section of the kernel, you will need to give the bootloader the exact memory address of the start of the text section.

Point is, to write kernel code, you need to know the memory addresses of the different sections.

The linker script lets you tell the linker the exact memory addresses where you want it to place the different elf sections. This way, you can make the linker point to the same memory addresses used in your code. You can be assured that the pointers in your code are pointing to some place that you KNOW.

And the good thing is that the linker lets you label this known memory points using variables.

If you let the linker decide the memory addresses,you would have to constantly change your code to point to the addresses the linker chose for you. And the linker is not that deterministic. Today it places the heap here, tomorrow there.

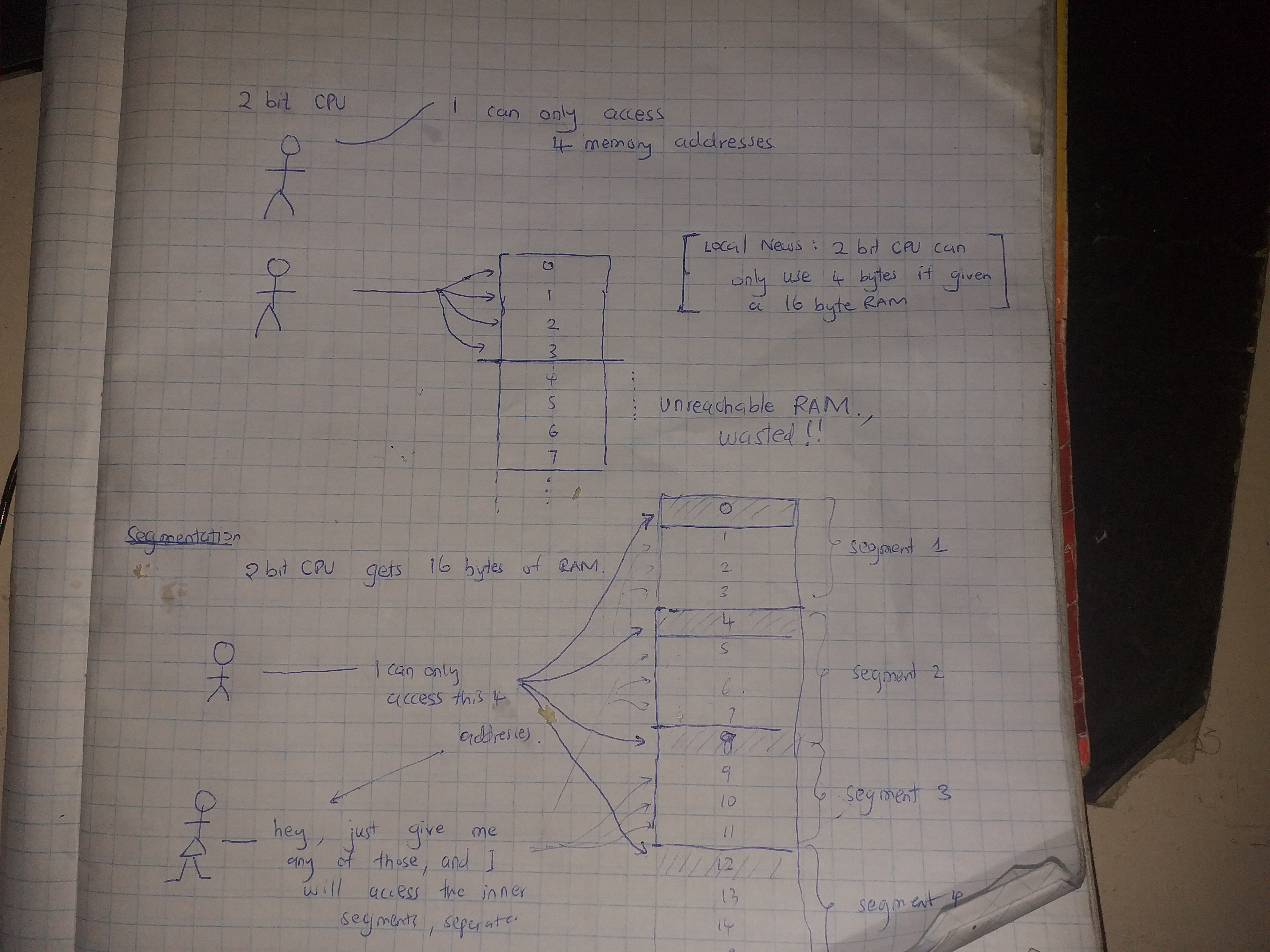

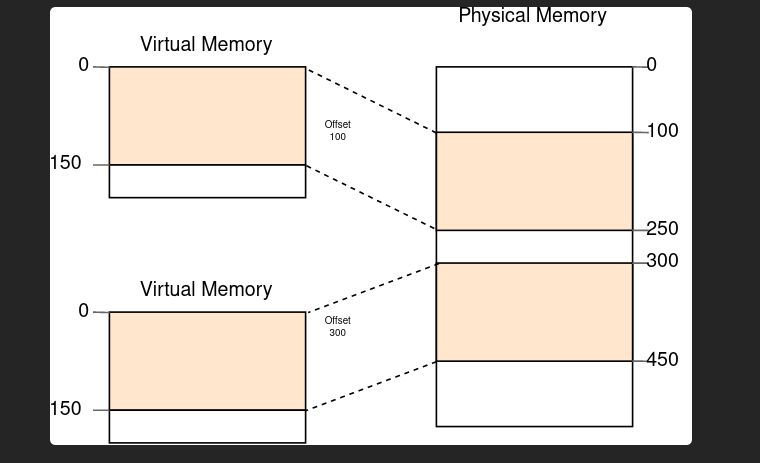

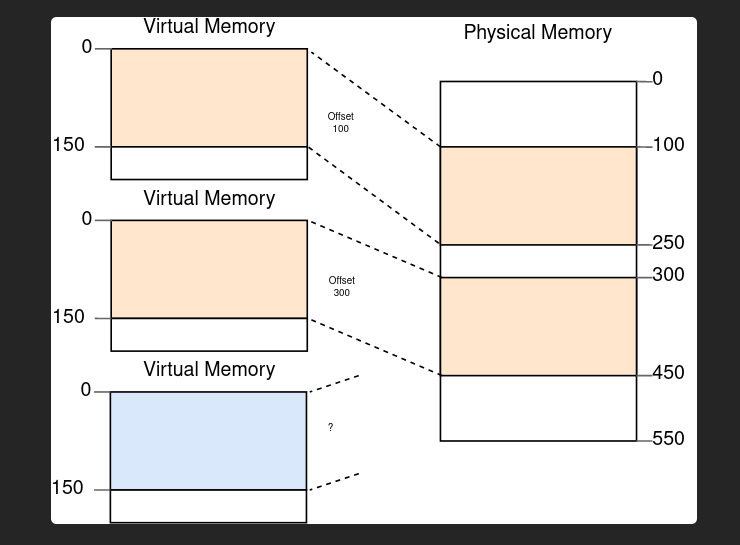

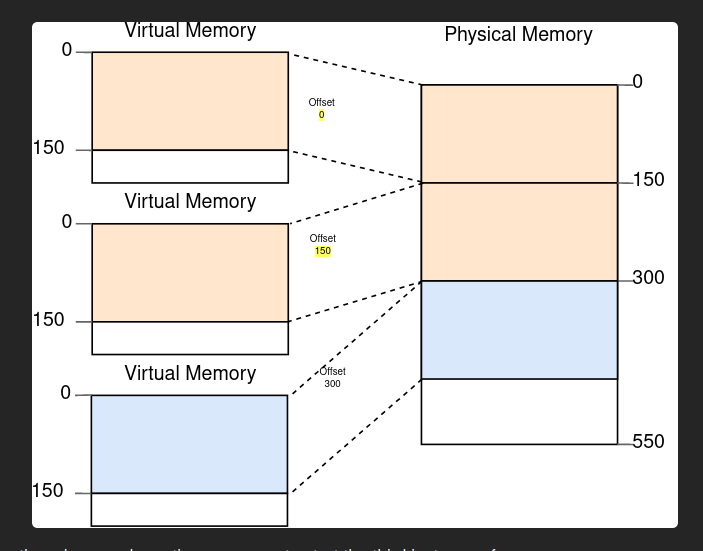

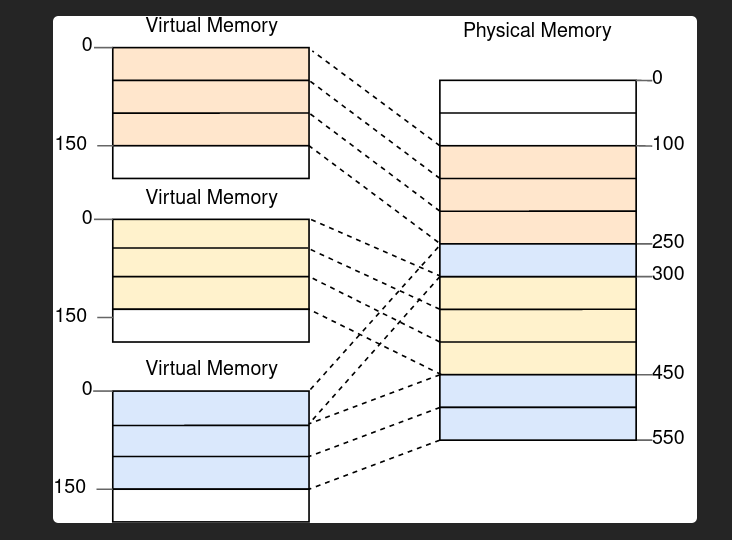

There is a problem with this explanation, the linker only deals with virtual memory. Not Physical memory. It is the job of the BIOS to load the kernel in physical addresses that mao to the virtual addresses.

Reason 3: You may want to make sure the different elf sections are aligned to a certain multiple. For example, if you plan to divide the heap into 4KB blocks, you may prefer to make the heap_start memory address a multiple of 4096

End of reasons...

So how do we write a Linker Script? And to which linker are we scripting for?

Which linker are we scripting for?

The rust gives you an option to choose whichever linker you want to use.

Rust uses the LLVM Linker by default. So we are currently scripting for the LLVM Linker.

You may want to use other linkers based on your usecase. For example the LLVM linker is known for its advanced optimizations. The gold linker is optimized for elf files only, so it is lightweight and faster than the GNU linker. Meaning that you will not prefer the gold linker when creating non_elf files.

To know which linker you are currently using, you can enter the command below :

rustc --version --verbose

You get a result like this : rustc 1.70.0-nightly (f63ccaf25 2023-03-06) binary: rustc commit-hash: f63ccaf25f74151a5d8ce057904cd944074b01d2 commit-date: 2023-03-06 host: x86_64-unknown-linux-gnu release: 1.70.0-nightly LLVM version: 15.0.7

From the above result, you can see That LLVM linker is used and specifically version 15.0.7

But each target uses a particular linker flavour, what if you want more information about your current host target? What if you want information about another non_host target ? Use the following command :

rustc +nightly -Z unstable-options --target=wasm32-unknown-unknown --print target-spec-json // for the nightly compiler

OR

rustc -Z unstable-options --target=riscv64gc-unknown-none-elf --print target-spec-json //for the stable compiler

You can optionaly specify your linker choice in the build manifest file (configuration file) - cargo.toml as follows :

[target.'cfg(target_os = "linux")'.llvm]

linker = "/usr/bin/ld.gold" //this specifies the path to the gold linker

But this is hard work, we are not taking that path. The less configurations we do, the more portable our code, the less headaches we get.

How do we write a Linker Script?

Before we explain how to write the linker script, we should answer the question : "Why write the liner script?"

The linker functions include :

- Resolving External symbols

- Section Merging

- Section Placement

We are writing the linker script so that we can instruct the linker on how it will do the section merging and section placement.

Section merging is the process of combining similar elf sections from different files: For example if A.o and B.o were to be linked together to form C.o then the linker will merge the .text section in both A and B ie. A.text_section + B.text_section = C.text_section

Section placement is the process of specifying the virtual address of the different sections within the elf file. For example you may place the text section at 0x00 or 0x800... you name it. By default the linker places the different segments in adjacent to each other... but if you do this section placement process manually, you can set paddings between segments or jumble things up.

You can follow this tutorial here :

- Tell the linker which architecture you are targeting

- You define the entry address of the elf file

- Define all the memory that we have : RAM and ROM or just one of them

Here is the Linker script example :

/*

define the architecture that the linker understands.

for any RISC-V target (64-bit riscv is the name of the architectut or 32-bit).

We will further refine this by using -mabi=lp64 and -march=rv64gc

*/

OUTPUT_ARCH( "riscv" )

/*

We're setting our entry point to a symbol

called _start which is inside of boot.S. This

essentially stores the address of _start as the

"entry point", or where CPU instructions should start

executing.

In the rest of this script, we are going to place _start

right at the beginning of 0x8000_0000 because this is where

the virtual machine and many RISC-V boards will start executing.

*/

ENTRY( _start )

/*

The MEMORY section will explain that we have "ram" that contains

a section that is 'w' (writeable), 'x' (executable), and 'a' (allocatable).

We use '!' to invert 'r' (read-only) and 'i' (initialized). We don't want

our memory to be read-only, and we're stating that it is NOT initialized

at the beginning.

The ORIGIN is the memory address 0x8000_0000. If we look at the virt

spec or the specification for the RISC-V HiFive Unleashed, this is the

starting memory address for our code.

Side note: There might be other boot ROMs at different addresses, but

their job is to get to this point.

Finally LENGTH = 128M tells the linker that we have 128 megabyte of RAM.

The linker will double check this to make sure everything can fit.

The HiFive Unleashed has a lot more RAM than this, but for the virtual

machine, I went with 128M since I think that's enough RAM for now.

We can provide other pieces of memory, such as QSPI, or ROM, but we're

telling the linker script here that we have one pool of RAM.

*/

MEMORY

{

ram (wxa!ri) : ORIGIN = 0x80000000, LENGTH = 128M

}

/*

PHDRS is short for "program headers", which we specify three here:

text - CPU instructions (executable sections)

data - Global, initialized variables

bss - Global, uninitialized variables (all will be set to 0 by boot.S)

The command PT_LOAD tells the linker that these sections will be loaded

from the file into memory.

We can actually stuff all of these into a single program header, but by

splitting it up into three, we can actually use the other PT_* commands

such as PT_DYNAMIC, PT_INTERP, PT_NULL to tell the linker where to find

additional information.

However, for our purposes, every section will be loaded from the program

headers.

*/

PHDRS

{

text PT_LOAD;

data PT_LOAD;

bss PT_LOAD;

}

/*

We are now going to organize the memory based on which

section it is in. In assembly, we can change the section

with the ".section" directive. However, in C++ and Rust,

CPU instructions go into text, global constants go into

rodata, global initialized variables go into data, and

global uninitialized variables go into bss.

*/

SECTIONS

{

/*

The first part of our RAM layout will be the text section.

Since our CPU instructions are here, and our memory starts at

0x8000_0000, we need our entry point to line up here.

*/

.text : {

/* In the GNU Linker Script Language, the PROVIDE keyword instructs the linker to declare a new symbol and assign it a value

PROVIDE allows me to create a symbol called _text_start so

I know where the text section starts in the operating system.

This should not move, but it is here for convenience.

The period '.' tells the linker to set _text_start to the

CURRENT location ('.' = current memory location). This current

memory location moves as we add things.

*/

PROVIDE(_text_start = .);

/*

We are going to layout all text sections here, starting with

.text.init.

The asterisk in front of the parentheses means to match

the .text.init section of ANY object file. Otherwise, we can specify

which object file should contain the .text.init section, for example,

boot.o(.text.init) would specifically put the .text.init section of

our bootloader here.

Because we might want to change the name of our files, we'll leave it

with a *.

Inside the parentheses is the name of the section. I created my own

called .text.init to make 100% sure that the _start is put right at the

beginning. The linker will lay this out in the order it receives it:

.text.init first

all .text sections next

any .text.* sections last

.text.* means to match anything after .text. If we didn't already specify

.text.init, this would've matched here. The assembler and linker can place

things in "special" text sections, so we match any we might come across here.

*/

*(.text.init) *(.text .text.*)

/*

Again, with PROVIDE, we're providing a readable symbol called _text_end, which is

set to the memory address AFTER .text.init, .text, and .text.*'s have been added.

*/

PROVIDE(_text_end = .);

/*

The portion after the right brace is in an odd format. However, this is telling the

linker what memory portion to put it in. We labeled our RAM, ram, with the constraints

that it is writeable, allocatable, and executable. The linker will make sure with this

that we can do all of those things.

>ram - This just tells the linker script to put this entire section (.text) into the

ram region of memory. To my knowledge, the '>' does not mean "greater than". Instead,

it is a symbol to let the linker know we want to put this in ram.

AT>ram - This sets the LMA (load memory address) region to the same thing.this linker script, we're loading

everything into its physical location. We'll l LMA is the final

translation of a VMA (virtual memory address). With et the kernel copy and sort out the

virtual memory. That's why >ram and AT>ram are continually the same thing.

:text - This tells the linker script to put this into the :text program header. We've only

defined three: text, data, and bss. In this case, we're telling the linker script

to go into the text section.

*/

} >ram AT>ram :text

/*

The global pointer allows the linker to position global variables and constants into

independent positions relative to the gp (global pointer) register. The globals start

after the text sections and are only relevant to the rodata, data, and bss sections.

*/

PROVIDE(_global_pointer = .);

/*

Most compilers create a rodata (read only data) section for global constants. However,

we're going to place ours in the text section. We can actually put this in :data, but

since the .text section is read-only, we can place it there.

NOTE: This doesn't actually do anything, yet. The actual "protection" cannot be done

at link time. Instead, when we program the memory management unit (MMU), we will be

able to choose which bits (R=read, W=write, X=execute) we want each memory segment

to be able to do.

*/

.rodata : {

PROVIDE(_rodata_start = .);

*(.rodata .rodata.*)

PROVIDE(_rodata_end = .);

/*

Again, we're placing the rodata section in the memory segment "ram" and we're putting

it in the :text program header. We don't have one for rodata anyway.

*/

} >ram AT>ram :text

.data : {

/*

. = ALIGN(4096) tells the linker to align the current memory location (which is

0x8000_0000 + text section + rodata section) to 4096 bytes. This is because our paging

system's resolution is 4,096 bytes or 4 KiB.

As a result, the current memory address is rounded off to the next nearest address that has a value that is a multiple of 4096

*/

. = ALIGN(4096);

PROVIDE(_data_start = .);

/*

sdata and data are essentially the same thing. However, compilers usually use the

sdata sections for shorter, quicker loading sections. So, usually critical data

is loaded there. However, we're loading all of this in one fell swoop.

So, we're looking to put all of the following sections under the umbrella .data:

.sdata

.sdata.[anything]

.data

.data.[anything]

...in that order.

*/

*(.sdata .sdata.*) *(.data .data.*)

PROVIDE(_data_end = .);

} >ram AT>ram :data

.bss : {

PROVIDE(_bss_start = .);

*(.sbss .sbss.*) *(.bss .bss.*)

PROVIDE(_bss_end = .);

} >ram AT>ram :bss

/*

The following will be helpful when we allocate the kernel stack (_stack) and

determine where the heap begins and ends (_heap_start and _heap_start + _heap_size)/

When we do memory allocation, we can use these symbols.

We use the symbols instead of hard-coding an address because this is a floating target.

Floating target means that the address space layout keeps on changing, do it becomes hard to hardcode physical adresses.

The heap size is not known at compile time

As we add code, the heap moves farther down the memory and gets shorter.

_memory_start will be set to 0x8000_0000 here. We use ORIGIN(ram) so that it will take

whatever we set the origin of ram to. Otherwise, we'd have to change it more than once

if we ever stray away from 0x8000_0000 as our entry point.

*/

PROVIDE(_memory_start = ORIGIN(ram));

/*

Our kernel stack starts at the end of the bss segment (_bss_end). However, we're allocating

0x80000 bytes (524 KiB) to our kernel stack. This should be PLENTY of space. The reason

we add the memory is because the stack grows from higher memory to lower memory (bottom to top).

Therefore we set the stack at the very bottom of its allocated slot.

When we go to allocate from the stack, we'll subtract the number of bytes we need.

*/

PROVIDE(_stack = _bss_end + 0x80000);

PROVIDE(_memory_end = ORIGIN(ram) + LENGTH(ram));

/*

Finally, our heap starts right after the kernel stack. This heap will be used mainly

to dole out memory for user-space applications. However, in some circumstances, it will

be used for kernel memory as well.

We don't align here because we let the kernel determine how it wants to do this.

*/

PROVIDE(_heap_start = _stack);

PROVIDE(_heap_size = _memory_end - _stack);

}

Our Linker script is ready !!!

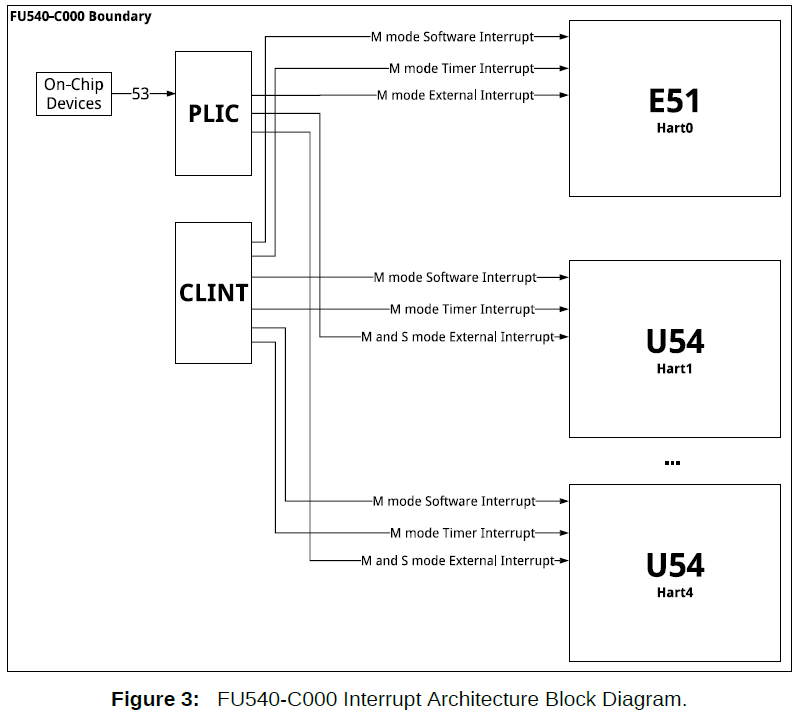

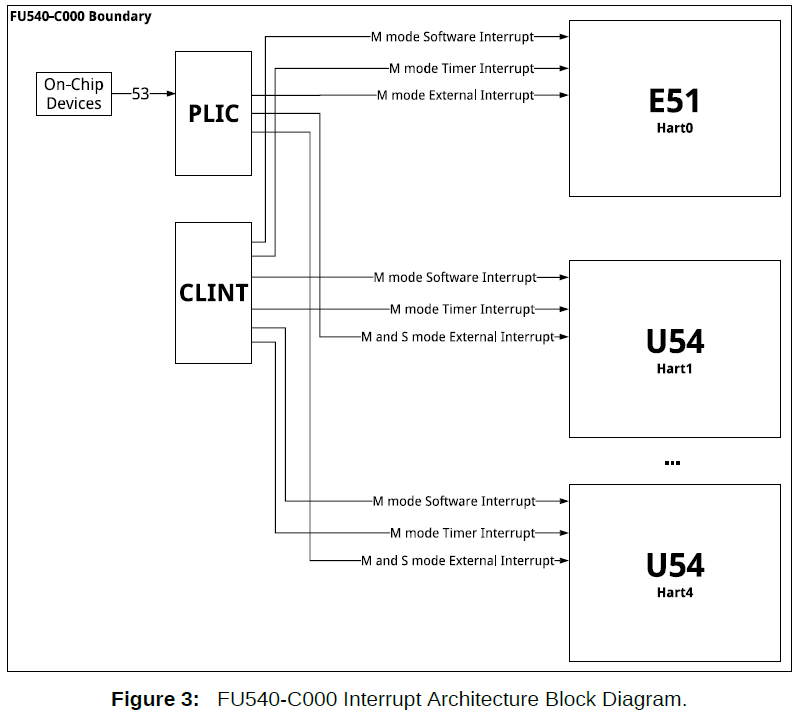

Setting up the Riscv Virtual environment

We will be using the Qemu RISC-V System emulator to emulate a RISCV-CPU microcontroller.

How to install Qemu RISCV system Emulator on Linux-Mint

At the command type

sudo apt install qemu-user

sudo apt install qemu-system-misc

Qemu Configurations

For QEMU’s RISC-V system emulation, you must specify which board model you want to emulate with the -M or --machine option; there is no default. In our case we will emulate the ‘virt’ Generic Virtual Platform as our target board model

When using the sifive_u or virt machine there are three different firmware boot options:

- -bios default - This is the default behaviour if no -bios option is included. This option will load the default OpenSBI firmware automatically. The firmware is included with the QEMU release and no user interaction is required. All a user needs to do is specify the kernel they want to boot with the -kernel option

- -bios none - QEMU will not automatically load any firmware. It is up to the user to load all the images they need.

- -bios --file - Tells QEMU to load the specified file as the firmware.

We will use the following Qemu configurations ;

// we define some variables

QEMU=qemu-system-riscv64 // we are using the Riscv Qemu emulator. qemu-system-riscv64 is a variable containing the path to the QEMU executable

MACH=virt // we will target the Virt Riscv Machine

CPU=rv64 // we will use a 64-bit CPU

CPUS=4 // The Board will have 4 CPUs... 4 HARTS

MEM=128M // The RAM memory will be 128 MBs

DRIVE=hdd.dsk // This is the path to our virtual harddrive

$(QEMU) -machine $(MACH)

-cpu $(CPU)

-smp $(CPUS) // specifies the number of CPUs to emulate

-m $(MEM) // specifies the amount of RAM in MBs

-nographic // disables graphical output, so QEMU runs in a terminal window.

-serial mon:stdio // connects the virtual machine motherboard's serial port to the host's system terminal. Ie, our Linux terminal. This enables us to use the terminal as a console to the virtual machine.

-bios none // we not depend on any firmware becaue our machine is virtual. We can just direclty load the OS image to memory.

-kernel $(OUT) // This specifies the path to the kernel image file

-drive if=none,format=raw,file=$(DRIVE),id=attic // explained below

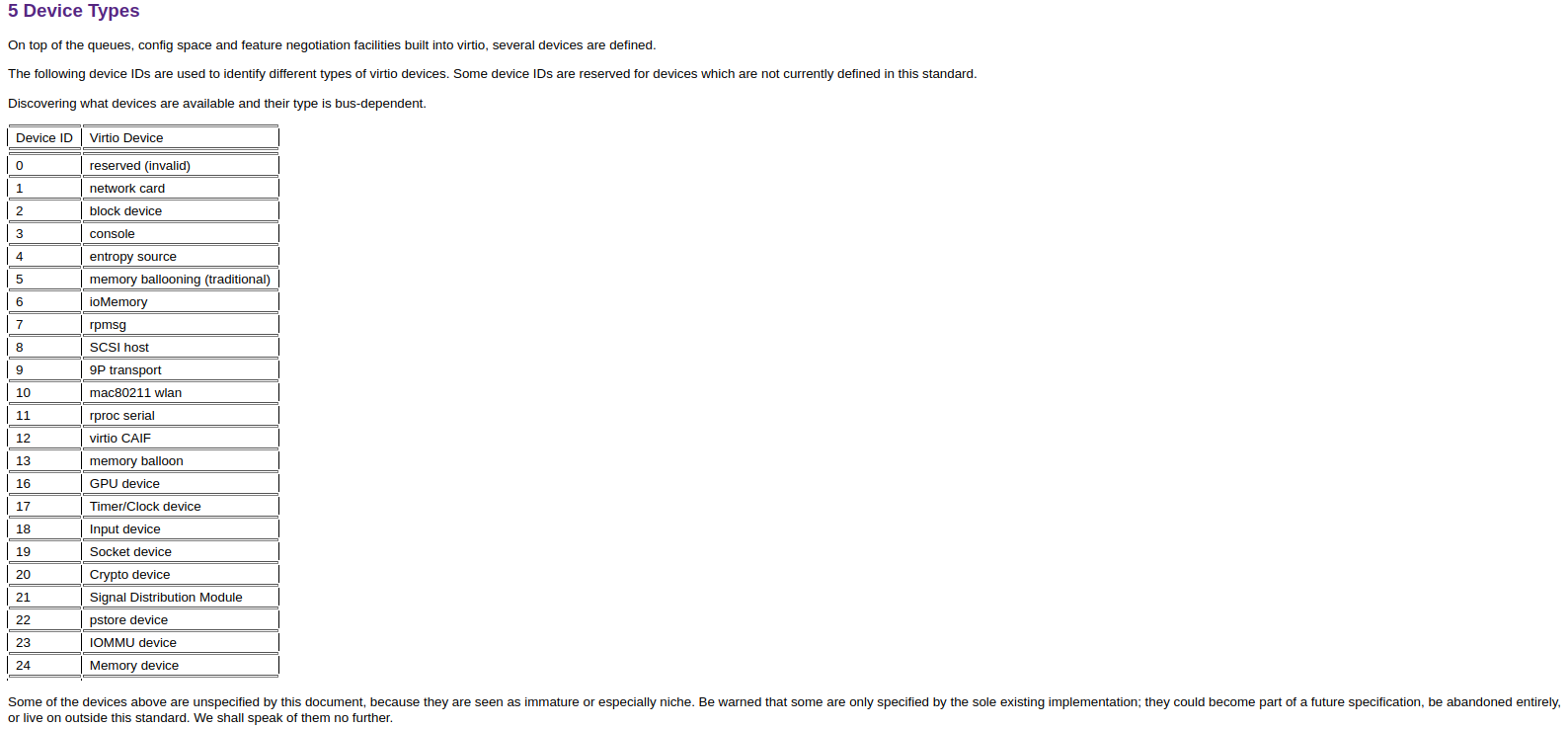

-device virtio-blk-device,scsi=off,drive=attic // explained below

-drive if=none,format=raw,file=$(DRIVE),id=attic

'if=none' meant that Qemu should not create an interface between the hard drive and the Kernel image. An example of an interface is SATA interface.

'format=raw' means that the hard drive image should consist of raw bytes to represent data on the disk. The disk should no have extra metadata or compressions. Other possible values for the format option include:

- qcow2: This is the default format for disk images in QEMU/KVM, and it supports features like compression, snapshots, and encryption.

- mdk: This is a format used by VMware virtualization software.

- vpc: This is a format used by Microsoft Virtual PC.

- raw: This is similar to format=raw, but it includes a 512-byte header that specifies the disk geometry and other information.

The choice of disk image format depends on the specific needs of your virtualization environment. For example, if you need to support snapshots or compression, you would likely choose qcow2. If you need to import or export the image to another virtualization platform, you may need to choose a format that is compatible with that platform.

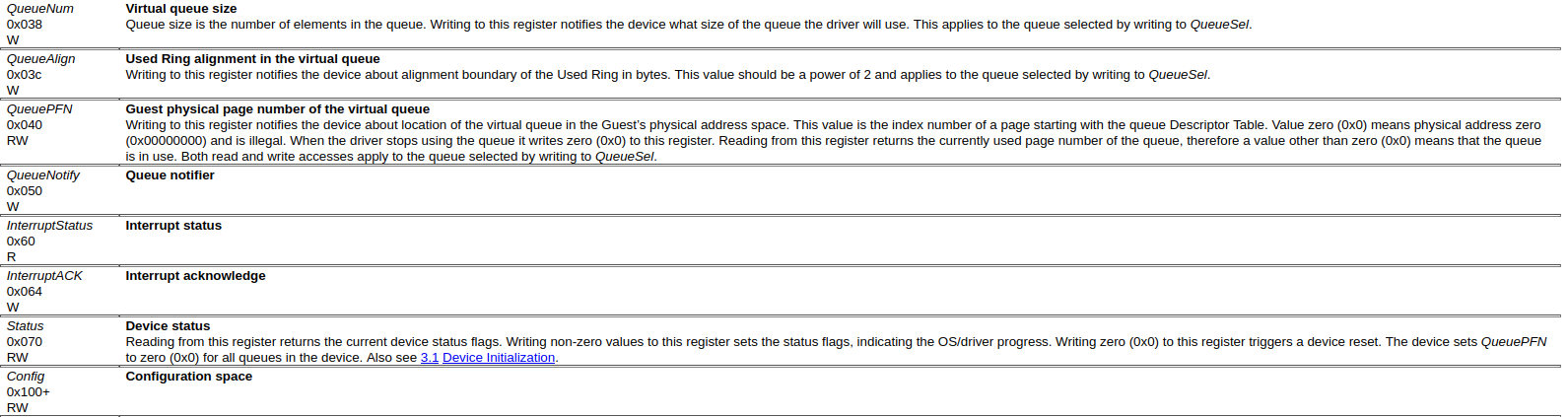

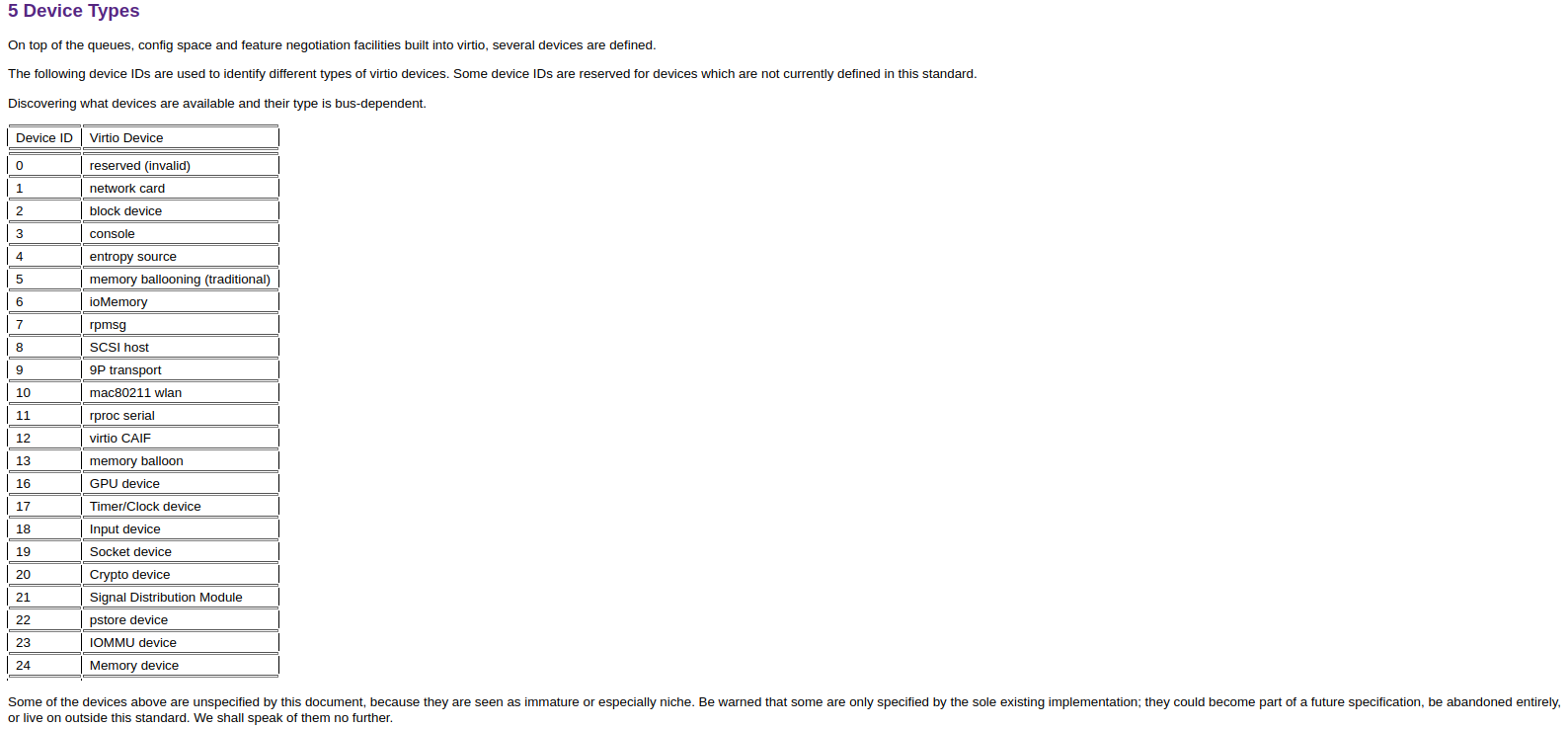

-device virtio-blk-device,scsi=off,drive=attic

'-device' is a Qemu command for attaching new devices to the motherboard of the virtual machine.

virtio-blk-device,scsi=off,drive=attic implies that we are adding a block device that adheres to VIRTIO protocol. 'scsi=off' disables the SCSI (Small Computer System Interface), this is because we intend to write a custom virtio block driver. 'drive=attic' specifies the Identifier of the new device that is being attached.

Creating a virtual hard disk

In the configurations above, it was specified that a virtual hard disk would get attached to the motherboard. It was specified that its path would be ./hdd.dsk

To create this hard disk we use a tool called Losetup. This tool converts a normal text file into a virtual block hard drive.

Losetup creates Loop devices. A loop device is a file that emulates a block device.

Losetup comes pre-installed in any standard linux distribution. To check its documentation, type this in the terminal:

man losetup

To create a virtual disk within your development working dierctory, write the following command in your terminal:

dd if=/dev/zero of=hdd.dsk count=32 bs=1M

where :

- 'if=/dev/zero: This option specifies the input file to use for the dd command. In this case, the input file is /dev/zero, which is a special file that produces an endless stream of zeroes when read.

- of=hdd.dsk: This option specifies the output file to create for the dd command. In this case, the output file is called hdd.dsk.

- count=32: This option specifies the number of blocks to copy from the input file to the output file. In this case, 32 blocks of data will be copied.

- bs=1M: This option specifies the block size to use for the dd command. In this case, the block size is 1 megabyte (1M).

An alternative set of commands would be :

fallocate --length 32M hdd.dsk // create a new file called hdd.dsk and allocate to it 32 MB

sudo losetup /dev/loop0 hdd.dsk // convert hdd.dsk into a virtual hard drive whose mount point is at /dev/loop0

Setting up the Build automation tool

Our build tool will be cargo.

We will not use third party build tools like Makefiles.

It is better to not use 3rd parties.

So create a .cargo folder withing the repo.

Create a config.toml inside the folder

So you have : project/.cargo/config.toml. Inside this file, paste the following configurations :

[build]

target = "riscv64gc-unknown-none-elf"

rustflags = ['-Clink-arg=-Tsrc/lds/virt.lds']

[target.riscv64gc-unknown-none-elf]

runner = "qemu-system-riscv64 -machine virt -cpu rv64 -smp 4 -m 128M -drive if=none,format=raw,file=hdd.dsk,id=attic -device virtio-blk-device,scsi=off,drive=attic -serial mon:stdio -nographic -bios none -kernel "

The [build] section has configs that affect the compilation process. We tell the compiler our target platform. And tell the linker the path to the linker script.

The [target.riscv64gc-unknown-none-elf] section has the configs that will be considered only if we are compiling for the riscv64gc-unknown-none-elf target.

THe "runner" specifies the cmd command that will be executed when we call "Cargo run". There is a space after -kernel. This is because cargo will automatically specify the executable, whose name is configured through Cargo.toml.

writing_a_bare_metal_rust_executable

references :

- https://os.phil-opp.com/minimal-rust-kernel/#a-minimal-kernel

1. NO_STD

A bare metal executable is a rust program that can run on a piece of hardware without needing an operating system.

Since we are building our own operating system, we need to write it as a program that is not dependent on another operating system.

Normal Rust programs depend on the rust standard library. The Rust standard library itself contains functions that call OS-specific system calls. So we cannot use the Rust std library.

We use the core Rust Library which is not OS-specific.

we add the attribute #![no_std]

2. NO_MAIN

Libc is a common C standard library that has been in use for a long time. It has been implemented for very many operating systems.

Rust is a new language. It is very hard to implement the rust_std for all operating systems. To save on labour and allow compatibility, Rust creators decided to make the Rust Library to use libC functions instead of recreating the functions in pure Rust. Though there are some parts of the Rust std library that do not depend on libc.

Now that it is clear that rust_std depends on libc, when a rust bin is executed, the following events happen.

- The executable program is stored in memory

- The CPU points to the first instruction of the executable (the etry point). In this case, the entry point is the C runtime.

- The C runtime sets up its environment in preparation for the libc functions that will get called by the rust_std functions

- After the C runtime has set up the execution environment for the libc functions, it points to the entry point of the Rust Runtime.

- The entry point of the Rust Runtime is marked with a language item called "start" ie [start]

- So the Rust runtime creates an executable environment for executing the Rust functions.

- After the Rust runtime has finished setting up things, it looks for the "main" function.

- Main starts executing

Our bare metal program does not depend on the C runtime. So this sequence of events is quite irrelevant to us.

What we will do is that we will inform the compiler that we wont follow this sequence by #![no_main] and then declare our own entry point.

To declare our own entry point, we will export a function out of the crate... like so :

#![allow(unused)] fn main() { #[no_mangle] pub extern "C" fn _start() }

But that is not enough, we need to tell the linker the name of our entry_point function. We do this by writing a linker script.

The linker will place the code as the first part of the .text section and update the elf header sections to reflect this info.

...

OUTPUT_ARCH( "riscv" )

ENTRY( _start )

MEMORY

{

ram : ORIGIN = 0x80000000, LENGTH = 128M

}

3. Panic Handler

Rust panics when a violatio happens. Rust requires you to define a function that will always get called after a panic happens.

That function is tagged by the #[panic_handler] attribute

The panic_handler function never returns anything, it diverges

#![allow(unused)] fn main() { use core::panic::PanicInfo; #[panic_handler] fn my_custom_function( panic_info: &PanicInfo)-> !{ println!("message : {}", panic_info.message()) println!("location : {}", panic_info.location()) } }

4. The eh_personality (aka error_handling personality)

Rust requires you to define a function that will always get called when it wants to unwind and free a stack.

This function is tagged with #[eh_personality] attribute.

When a panic happens, the program stops (theoretically). The program can decide to free the stack or just abort and let the underlying OS clear the stack.

The thing is, to clear the stack, you have to unwind it. To unwind the stack, you have to use some hard functions...Functions that depend on some OS functionalities. This is a chicken-egg problem.

So we resort to aborting.

To specify this behaviour, you can tweak the cargo file as follows :

[profile.release]

panic = "abort"

[profile.dev]

panic = "abort"

By default the settings are usually :

[profile.release]

panic = "unwind"

[profile.dev]

panic = "unwind"

Now, the #[eh_personality] tag is a tag that is pegged to the function that gets called when a rust program wants to unwind its stack. eg

#![allow(unused)] fn main() { #[eh_personality] fn custom_unwind(){ // do some unwinding statements ... MAgiC! } }

BUT since we have specified that our program will always abort... AND that it will never call the unwind function, we are no longer required to define the unwinding function

5. Compile to a bare_metal target

[undone]

boot_design

Boot Design

The boot program is the one that is responsible for :

- Setup the environment for the kernel to run in machine mode

- Transfer the control to kinit() (kernel running in machine mode)

- Designate a specific place where the CPU will jump to if a trap occurred when kernel is in either machine mode or supervisor mode.

- Initiate an environment for the kernel to run in supervisor mode.

- the boot code is the one that contains the _start function. _start function is the entry point for the whole kernel image. So it is the first place the CPU points to in the RAM after the Qemu firmware has done its thing.

Bird's View (ideal but not as implemented)

stateDiagram

load_firmware

load_bootloader

load_kernel

run_kernel

shutdown

state look_for_bootloader <<choice>>

state look_for_kernel <<choice>>

[*] --> load_firmware

load_firmware --> look_for_bootloader

look_for_bootloader --> load_bootloader : Bootloader is found

look_for_bootloader --> shutdown : Bootloader is missing

load_bootloader --> look_for_kernel

look_for_kernel --> load_kernel : Kernel image is found

look_for_kernel --> shutdown : Kernel image is Missing

load_kernel --> run_kernel

run_kernel --> shutdown

shutdown --> [*]

Assembly Glue

Instead of the boot code being a program that gets called once(as seen above), it becomes the glue code that gets called whenever kinit and kmain go out of scope. It encompases the entire kernel. It acts as glue code.

Detailed Program flow

graph TD

Qemu_virtual_firmware -->|Loads the kernel image|Booze

subgraph Booze

Start --> _choose_bootloading_HART

_choose_bootloading_HART --> C1{is it the wrong HART?}

C1 -->|Yes| Shutdown_specific_HART

Shutdown_specific_HART -->|probe next HART| C1

C1 -->|No| clear_BSS_section

clear_BSS_section --> _initialize_registers_for_kinit

_initialize_registers_for_kinit -->|Jump_to_kinit| kinit

kinit -->|returns back to Booze Glue| Glue

Glue --> _initialize_environment_for_kmain

_initialize_environment_for_kmain -->|initialization includes switching to S Mode| kmain

kmain -->|Happens ONLY if trap happens| Trap_handler

Trap_handler -->|handles trap, returns control| kmain

kmain -->|Happens only if kmain has finished all execution instructions| shutdown

end

Boot Design

The boot program is the one that is responsible for :

- Setup the environment for the kernel to run in machine mode

- Transfer the control to kinit() (kernel running in machine mode)

- Designate a specific place where the CPU will jump to if a trap occurred when kernel is in either machine mode or supervisor mode.

- Initiate an environment for the kernel to run in supervisor mode.

- the boot code is the one that contains the _start function. _start function is the entry point for the whole kernel image. So it is the first place the CPU points to in the RAM after the Qemu firmware has done its thing.

Bird's View (ideal but not as implemented)

stateDiagram

load_firmware

load_bootloader

load_kernel

run_kernel

shutdown

state look_for_bootloader <<choice>>

state look_for_kernel <<choice>>

[*] --> load_firmware

load_firmware --> look_for_bootloader

look_for_bootloader --> load_bootloader : Bootloader is found

look_for_bootloader --> shutdown : Bootloader is missing

load_bootloader --> look_for_kernel

look_for_kernel --> load_kernel : Kernel image is found

look_for_kernel --> shutdown : Kernel image is Missing

load_kernel --> run_kernel

run_kernel --> shutdown

shutdown --> [*]

Assembly Glue

Instead of the boot code being a program that gets called once(as seen above), it becomes the glue code that gets called whenever kinit and kmain go out of scope. It encompases the entire kernel. It acts as glue code.

Detailed Program flow

graph TD

Qemu_virtual_firmware -->|Loads the kernel image|Booze

subgraph Booze

Start --> _choose_bootloading_HART

_choose_bootloading_HART --> C1{is it the wrong HART?}

C1 -->|Yes| Shutdown_specific_HART

Shutdown_specific_HART -->|probe next HART| C1

C1 -->|No| clear_BSS_section

clear_BSS_section --> _initialize_registers_for_kinit

_initialize_registers_for_kinit -->|Jump_to_kinit| kinit

kinit -->|returns back to Booze Glue| Glue

Glue --> _initialize_environment_for_kmain

_initialize_environment_for_kmain -->|initialization includes switching to S Mode| kmain

kmain -->|Happens ONLY if trap happens| Trap_handler

Trap_handler -->|handles trap, returns control| kmain

kmain -->|Happens only if kmain has finished all execution instructions| shutdown

end

The Bootloader

For a long time I thought the way the CPU worked was some dark magic.

The CPU is an indiscriminate machine, it is just a bunch of circuits that repeatedly do the operations below from the moment the CPU is powered on :

- It reads the memory address storeed in the the program counter register. Let us call this memory address Address_X.

- Fetches the instruction pointed to by Address_X.

- Executes the instruction using one or more of its circuits/gates

- repeats infinitely

It is up to us to occasionally make the program counter to point to the instrutions we want executed.

To control this machine, we have to change the value in its control status registers.

When you look at it from this perspective, it no longer seems like dark magic.

It is a machine that can be controlled by modifying the value in relevant registers.

Each CPU comes with its own assembly language.

We will be using RISCV assembly to write the assembly code for the bootloader.

The definition of what a bootloader is supposed to do varies from OS to OS. For example, some bootloaders can perform hardware power_on tests while others just leave that work to the CPU firmware.

A typical bootloader essentially does the following operations:

- Find the memory address of the Kernel program by searching through the external memory devices that have been plugged into the Motherboard.

- Loads the Kernel image onto the RAM. Note that it only loads the required sections, it might not load the entire image.

- Prepare the values found in the CPU registers to suit the execution of the kernel. For example making the Stack pointer to point to the stack of the kernel.

- Transfering control to the kernel. This is done by making the program counter point to the entry_point of the kernel

The Bootloader in this chapter is much simpler. It does not have to look for the kernel image in a secondary memory like a hard-disk, instead, the Kernel and the bootloader are one program. The Basic Bootloader in this case is a software program that : - Finds the memory location of the kernel's entry_point (the first kernel instruction). This instruction address is still part of the bootloader. Remember that (Kernel + bootloader) == 1 united program - Loads the kernel image to memory - Transfers control to the kernel

The Bootloader has many definitions depending on the additional functionalities it has :

- Dealing with the convertion of CPI from real mode to protected mode and finally to 64-bit mode

- Having a user interface that gives its users the option to choose among multiple kernel images

- Having the bootloader code implemented in seperate parts.

- Having the bootloader do some tasks that were originally meant for the firmware eg. Power_on_self tests

We do not care about the above functionalities... for now.

The Boot process

References :

When the machine is powered on :

The Firmware

The CPU begins its fetch-execute cycle. Typically, the PC register of the CPU points to a memory address in the ROM.

The ROM contains hardcoded firmware code. In x86 this firmware can be BIOS or UEFI.

The firmware code performs Power-on-tests on all pluged devices.

The firmware code initializes the hardware : for example it maps the dedicated I/O MMIO memory and enumerates the RAM.

After setting up the execution environment, it scans the plugged in secondary memory devices... Depending on the partitioning scheme used in those devices, it looks for valid bootloaders. At this point some firmware give the user a chance to choose which bootloader they would prefer among the ones the firmware has discovered

The Bootloader

After the Firmware has set up the execution environment, It makes the CPU pointer ton point at the entr point of the boot_code.

In our case, the bootloader will do the following functions :

- Pick only one CPU to complete the execution of the bootloader code. This is because at the beginning we do not want any kind of paralellism. Moreover, the bootcode is a simple code that can easily be done by one CPU, adding parallelism increases unnecessary complexity. It means we will have to do interprocessor communications at the start. That is just unnecessary overengineering to save a nano_secog of a nanosecond of a nanosecond

- Clear the uninitialized memory sections : the heap and BSS section.

- Transfer control to the Kernel code found in memory

Bootloader pseudo code

algorithm inputs : No inputs

algorithm outputs : No outputs, it just calls another function that never returns.

-

set the necessary assembler directives

- notify the assembler that the code should not use compressed code

- define the memory sections - .text.init section : the .text.init section is different from other .text sections because the .text.init section contains initialization code that gets executed before the main function and other init sections. (.text.init) section must be executed before all other sections - .data section

-

Choose HART 0 as the main and only core that should continue to execute the boot_code

- if the Hart ID is not 0, subject that core to an endless sleep

-

Confirm that the HART is in machine mode

-

Clear the BSS section, we need no surprises.

-

Set up the regiters of the CPU to be ready to execute the kernel code

-

Call mret

-

Set up some general registers

- fetch the global pointer so that we ge to access the data sections more confidently, update the global_pointer register

- update the stack pointer to point to the bottom of the kernel stack

- update the return address to point to an Endless sleep function... the kernel should not return in the first place

-

Set up the control registers

- the mstatus register

- set previous MPP to Machine mode, this is because we intend to run the kernel in Machine mode for some time before moving to S-Mode. When we call mret instruction, the CPU will be run in the mode specified in MPP

- set MIE mstatus bit to 1, this enables the CPU to catch interrupts

- set MPIE mstatis bit to 1, this enables the kernel to be able to receive interrupts once we transfer cotrol to it using mret.

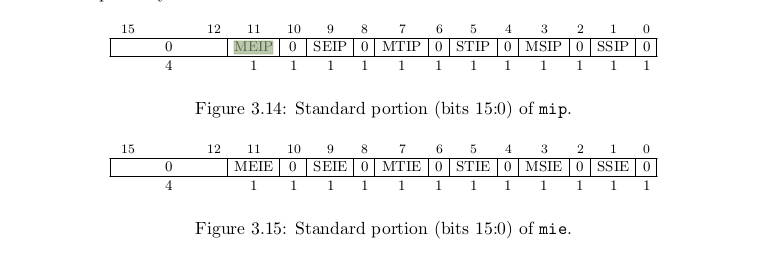

- The machine_interrupt_enable register

- enable all the interrupts (Software, Timer and external)

- the machine_trap_vector

- Let the mtvec register point to a trap vector point... defined globally in assembly language

- the MEPC should point to the kmain function

- the mstatus register

-

- Setup the CPU status to suit the jump to kernel code :

- set the medeleg register : we will not delegate any exception, we will handle all exceptions in Machine mode

- set the mideleg register : we will not delegate any interrupt to lower levels, we will handle all interrupts in Machine mode

- set the mstatus to allow software interrupts and external interrupts

- Set the MIE register to handle only

- set the stack pointer to point at the bottom of the stack

- set the mstatus register :

- allow interrups to be allowed in both machine mode and supervisor mode by setting the MPP(Machine Previous Protection) to the value 3

- set the MEPC ; machine exception program Counter to point to the kernel entry point.

- Set the MTVEC : Machine Trao Vector to point to the Exception handling code

- Call MRET

Why are we calling WFI?

We are calling the WFI instruction to put all the other CPU cores to sleep. Our OS only uses one HART (Cpu).

The WFI (Wait for interrupt instruction) - This RISCV instruction powers off the CPU and only leaves a small circiut running. THis circuit continuously checks if an interrupt signal has been sent to the powered off CPU. If an interrupt is detected, the CPU gets powered on. It is kind of a 'sleep' instruction. It can be used to save power when the CPU is idle. We are calling the WFI instruction to put all the other CPU cores to sleep. Our OS only uses one HART (Cpu).

Why are we disabling Riscv Compressed instruction?

- So that we gain simplicity in debugging.

In RISCV, the assembler usually encodes each assembly instruction into 32 bits. But this is not always the case, you can instruct the assembler to use compressed instructions. Compressed instructions are only 16 bits long. Not all assembly instructions get encoded to 16 bits... just a select few. This ensures memory efficient code.

However, it makes it hard to debug code because the not ALL instructions are 32 bits as before.

we achieve this by using either of the two assembly directives :

.option norvc // No RiscV compressed instructions

.option rvc // Yes to RiscV compressed instructions

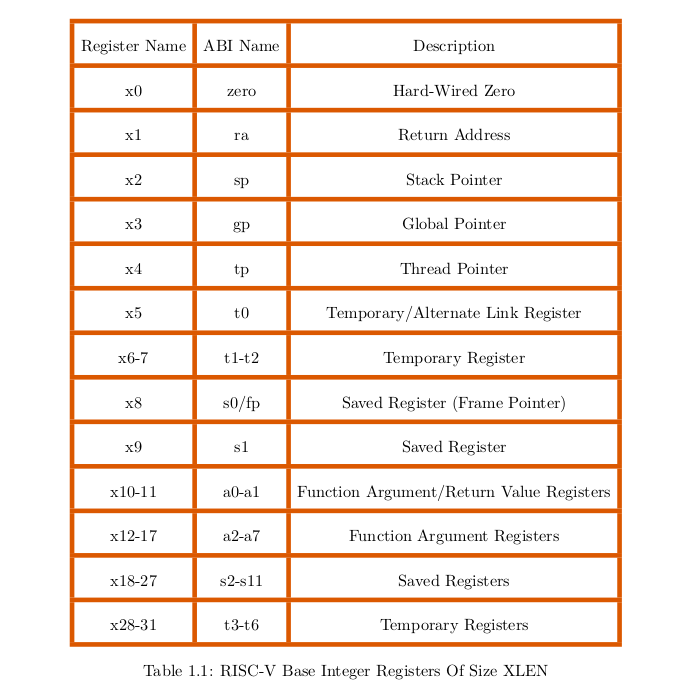

Why do we need to load the global pointer when writing the Bootloader? So that the bootloader code gets to use the correct global data associated to the Operating system image.

The global pointer references the base address of global data in the memory map.

To access any global data, you have to know the base address + offset.

The bootloader typically gets executed as a seperate program from the operating system. So the bootloader may have a different memory map from the memory map of the kernel.

Considering that the bootloader needs to use the operating system's global data, we make the global pointer that the bootloader references to be the gp found in the memory map of the kernel.

Now this operation is delicate; we are accessing another memory map to access global data that may or may not be the same as the data we are trying to change. We need to make this operation explicit, no surprises. So we temporarily kill all code optimizations when doing this operation by using the directives :

.option push // save previous assembly directives... because in the next few lines we may use contradicting directives

.option norelax // no optimization

.option pop // restore previous assembly directives

Designs

Initial Program Flow diagram

graph TD

A[Qemu ELF loader] -->|loads Elf file containing kernel loader| B[kernel Loader]

B --> |prepares the CPU registers for kernel, calls kernel entry point| C[Kernel Runs]

Kernel loader sequence of events

graph TD

A[set assembler directives] --> B[Look for HART 0] ;

B --> C{Is the Core HART 0?} ;

C -->|Yes| D[Clear Kernels BSS section];

C -->|No| E[Put HART to sleep];

D --> F[initialize CPU registers for kernel];

F --> G[summon kmain];

Qemu --> Boot --> kinit --> kmain

Kinit messes around with physical memory in Machine mode while kmain messes with virtual memory in Supervisor mode

Kinit gets us to kmain.

under kinit we do not accept any interrupts : This allows us to setup our machine without any disturbance from other cores or the PLIC

- we make mepc point to kinit

- we make the return address of kinit point to the asm funtion that will transition us to kmain ; kinit returns ()

- we call mret and jump into kinit rust

And what are we doing under kinit? here

- when kinit returns, we are on the function to transition to kmain

- we set the mstatus register

- set MPP to 01 (supervisor)

- set Previous machine interrupt-enable bit is 1 (MPIE=1 [Enabled])

- wet Previous interrupt-enable bit is 1 (SPIE=1 [Enabled]).

- setnputs : No inpu mtvec to mtrap_vector

- set mepc to kmain

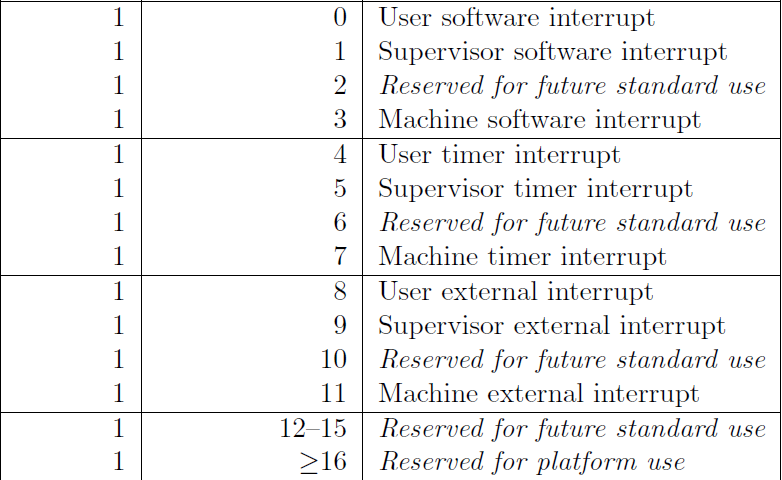

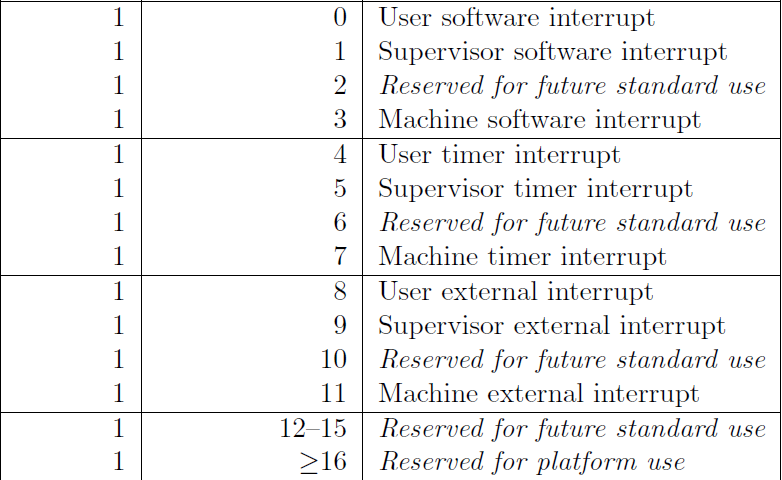

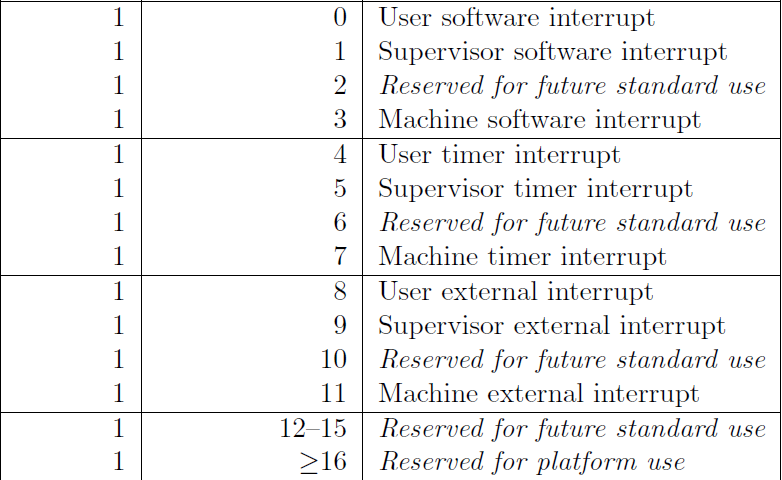

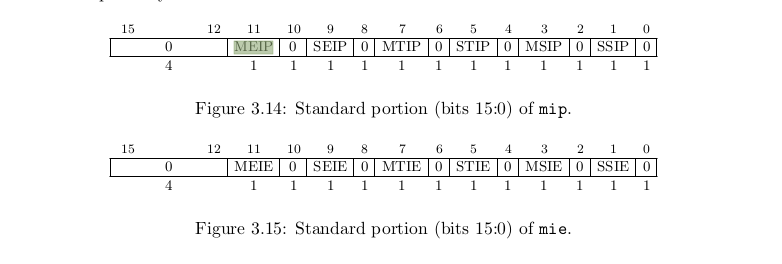

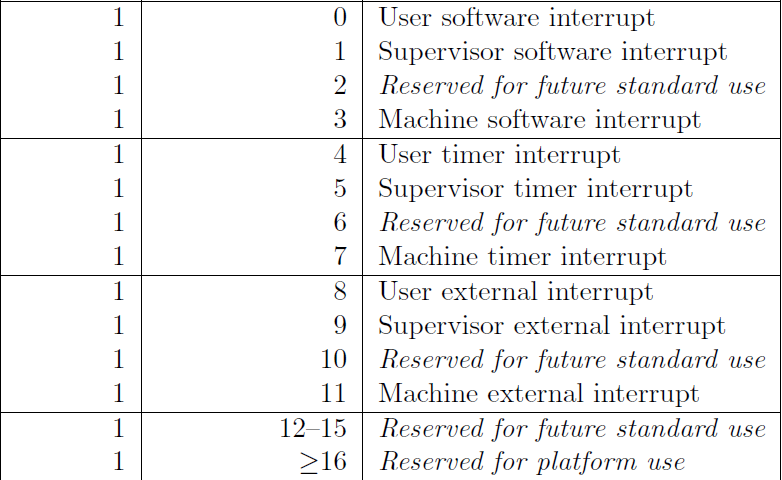

- set which specific interrupts are allowed by setting the MIE register

- 1 << 1 : Supervisor software interrupt enable (SSIE=1 [Enabled])

- 1 << 5 : Supervisor timer interrupt enable (STIE=1 [Enabled])

- 1 << 9 : Supervisor external interrupt enable (SEIE=1 [Enabled])

- 0xaaa = MEIP/SEIP and MTIP/STIP and MSIP/SSIP

- set return register to point to Shutdown. If main returns () ... shutdown

kinit

Before kinit make sure that all linker variables are accessible in Rust Make kinit global for the linker using "extern"

What does kinit do?

- initialize the UART system

- declare a single instance of the UART object

- initialize the UART instance (configure the UART registers for communication)

- Initialize the page allocator system

- clear the page destriptors in the heap

- define ALLOC_Start, where the Pages Start

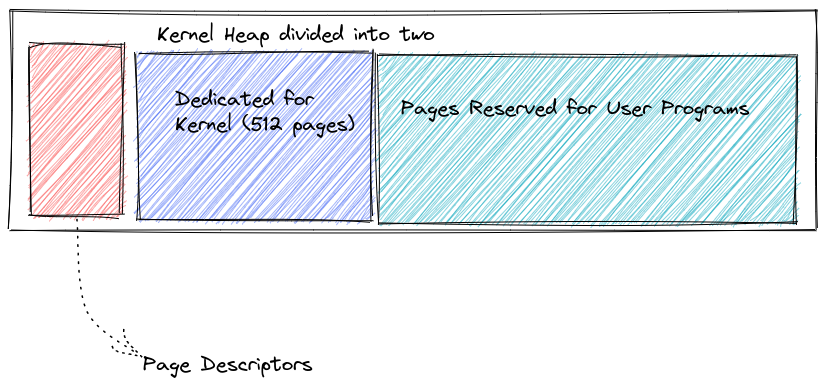

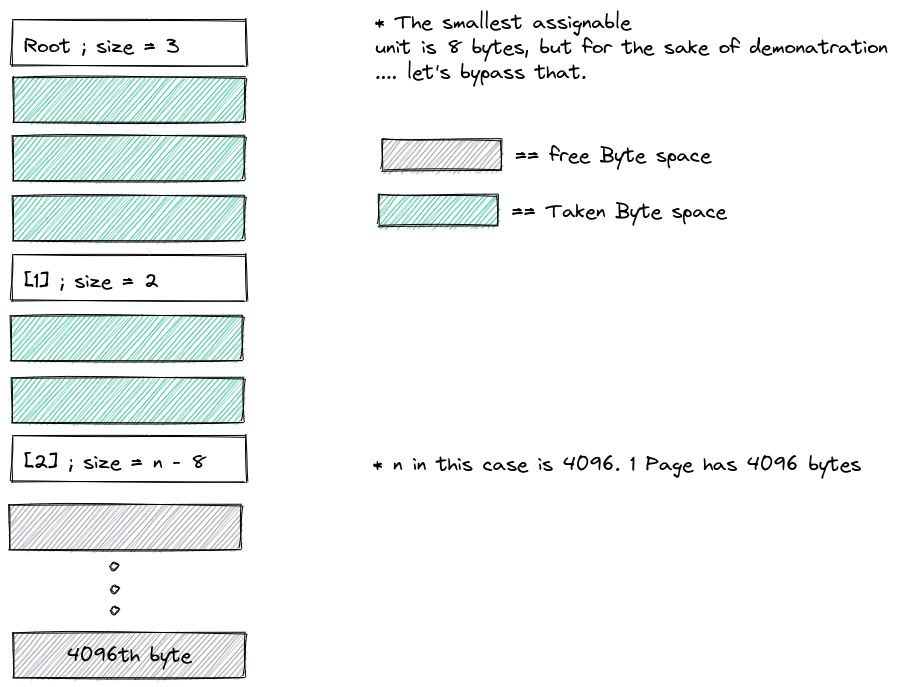

- Initialize byte allocation system (Borrow this)

- define the number of kernel pages (512 pages)

- create a kernel heap by allocating those pages, and zeroing them out

- set the first AllocStruct

- Allocate Space for the Root Page Table immediately after the kernel Heap

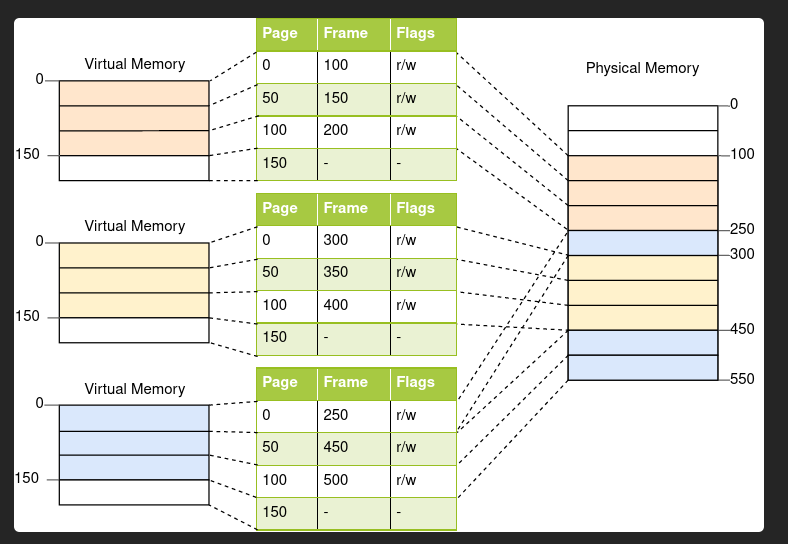

- Set up the values of the paging

- Get position of the root table that was created during kmem::init()

- Identity Map all the known kernel addresses specified in the linker script

- Map the Kernel Heap

- Map the UART

- Map the PLIC

- Map the CLINT

- Define the SATP value

- Define the address of the TRAP_FRAME for our current HART. Each HART gets one TRAP_FRAME (it is global)

- Store the address of the TRAP_FRAME in the mscratch register

- Store the address of the TRAP_FRAME in the sscratch register

- Map the TRAP_FRAME address for this HART

- initialize the page memory allocation system

Setting Up Communications

References :

- Chapter 3 : How to write Drivers for Peripherals

- Communications : the UART Driver

- The UART specifications

- The UART Datasheet

Our OS will communicate with peripherals. Peripherals are external devices...external cirtuits... things that are not originally part of the Motherboard.

In this chapter, the peripherals that we will be attaching will be the console for output and the keyboard for input.

The connection between the microcontroller and both of these peripherals is a serial connection.

I2C

- packet-wise, has start and stop bits. Not streaming

SPI

- continuous, not packet-wise. data does not have start and stop bits

- data can be transferred without interruption. Any number of bits can be sent or received in a continuous stream.... NOT packetwise

UART

- packet-wise, has start and stop bits. Not streaming

Designs and layouts

Birds Eye View

Keyboard Input - Level 0

Keyboard Input - Level 1

flowchart TD

START --> KeyBoard

KeyBoard -->|stream of bytes| Uart_upper_interface

Uart_upper_interface -->|Store bytes into| FIFO_Buffer

subgraph UART

FIFO_Buffer -->|check if buffer has new data| if_state{Does It?}

if_state -->|Yes| update_interrupt_status

if_state -->|No| Do_Nothing

FIFO_Buffer -->|check if all Buffer data has been read| if_state_2{Has It?}

if_state_2 -->|Yes| set_UART_as_write_ready

if_state_2 -->|Yes| stop_read_interrupt

if_state_2 -->|No| set_UART_as_read_ready

if_state_2 -->|No| update_RHR_register

update_RHR_register --> RHR_register

end

update_interrupt_status -->|Send read interrupt to PLIC| Plic

Plic -->|send interrupt to CPU| CPU

CPU -->|Summon trap handler| Trap_Handler

subgraph Trap_handling

Trap_Handler -->|Is the UART still read-ready?| if_state_4{Is it?}

if_state_4 ---->|Yes| Read_from_RHR_register

Read_from_RHR_register <--> RHR_register

if_state_4 -->|No| Then

Then -->|Tell Plic that interrupt has been sorted| Plic

Trap_Handler -->|Has reading from RHR been successful?| if_state_3{Has it?}

if_state_3 -->|Yes| store_word_into_stdin_buffer

store_word_into_stdin_buffer --> stdin_buffer

if_state_3 -->|No| Throw_exception

end

General Theory on communication

Serial and Parallel Communication

[undone] : define serial and parallel communication. Explain this info important?

Inside the motherboard circuit or the peripherals circuits, the internal components are connected using buses(parallel connections).

But the cables connecting these independent circuits are typically serial connections mostly because of the cost of creating cables that are wide.

Another reason is the simplicity in configuration using serial lines

[undone] : Image demonstrating the advantages/disadvantages of using parralel OR serial connections

| Parallel Connection | Serial Connection |

|---|---|

| parallel connection is expensive | serial connection is less expensive |

| parallel connection is fast | serial connection is less fast |

| parallel connection is hard to configure perfectly (you still need some agreed upon level of lines : You are boiling x number of lines to y lines today, tomorrow you may need to boil it down to z lines -- that is hectic) | serial conection is more universal in its configuration (you are boiling down x number of lines to 1 line -- ALWAYS) |

Parallel connection

parallel connection is expensive

parallel connection is fast

parallel connection is hard to configure perfectly (you still need some agreed upon level of lines : You are boiling x number of lines to y lines today, tomorrow you may need to boil it down to z lines -- that is hectic)

Serial Connection

serial connection is less expensive

serial connection is less fast

serial conection is more universal in its configuration (you are boiling down x number of lines to 1 line -- ALWAYS)

Theory of parallel to serial conversion

Before we discuss the actual Drivers and Registers, let's discuss the theory of parallel-to-serial conversion.

- On the Sender's side

The serializer gets configured by the host system. The baud rate is set, the size of a data frame is set and interrupt handling is configured.

The serializer hardware receives parallel input... let's say 8 bits.

The serializer sequentially pushes each bit of that parallel input into a shift register. Whether it begins from the Most Significant bit or the LSB is up to the specifications of the communication protocol being used.

The serializer packages the shift register bits as a data frame, with a startbit, a stop-bit and maybe a parity bit for error checking.

The serializer sequentially pushes the bits out of the shift register and into the transmission channel.

The way it pushes the bits into the line can be either FIFO or FILO.

The rate at which it pushes the bits into the transmission line is called the Baud Rate. It is measured in bits per second. In this case, baud rate is the same as bit rate because each bit change equals a bit transmission.

2 On the receiver's end

It is assumed that the receiver has the same configurations as the sender: same baud rate, same data_frame size.

The deserializer receives the serial data frame.

checks the parity bit for error detection

Communication Protocols

A protocol is a set of rules or specifications on how to do something.

In this case, the protocols we are talking about are protocols about converting parallel data signals into a serial signal.

There are many protocols, but our focus will be on the UART 'protocol'. The reason the name protocol is in quotes is because there is no standard UART protocol. The specifications implemented vary depending the UART devices and driver settings.

Why are we not using the USB driver/protocol?

The USB also does the conversion of parallel signals to serial signals. The USB has higher transfer speeds than the UART connection. The USB can do 20 Gbps while the UART does around 1 Mbps!

However, we will use the UART because of two reasons :

- Its simplicity in configuration. The UART is easier to configure when compared to the USB. This is a learning project, we cannot afford to delve into the complex nature of USBs.

- It uses less power than the USB. The project is targeting embedded systems; the less power our machine consumes, the better.

We trade-off the speed of the USB for the simplicity and power-efficiency of the UART.

The UART

[references]

- UART communication protocol - just read this

- https://www.analog.com/en/analog-dialogue/articles/uart-a-hardware-communication-protocol.html

Intro

The UART device is a hardware device that stands in between a parallel connection and a serial connection. It converts a serial signal to a parallel signal and vice-versa.

It stands between the motherboard and the peripheral devices that use serial connections ; eg mouse, keyboard and console output.

The UART driver is the software that controls and interacts with the physical UART device.

In the case of Qemu, the console output and the keyboard input use the same UART device. This is because the transmit_out channel is connected to the console output AND the receive channel is connected to the keyboard.

The UART Registers

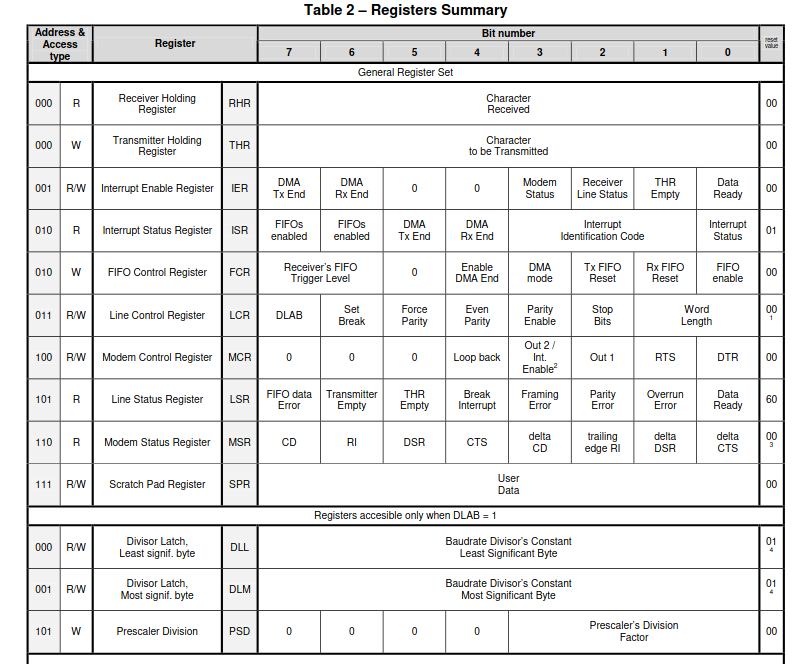

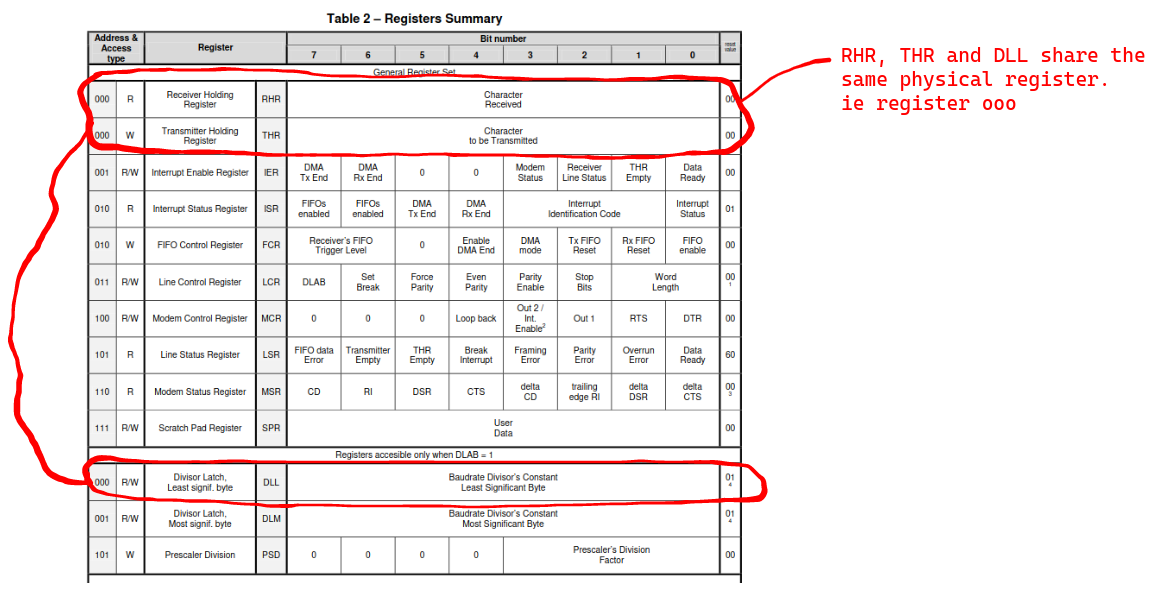

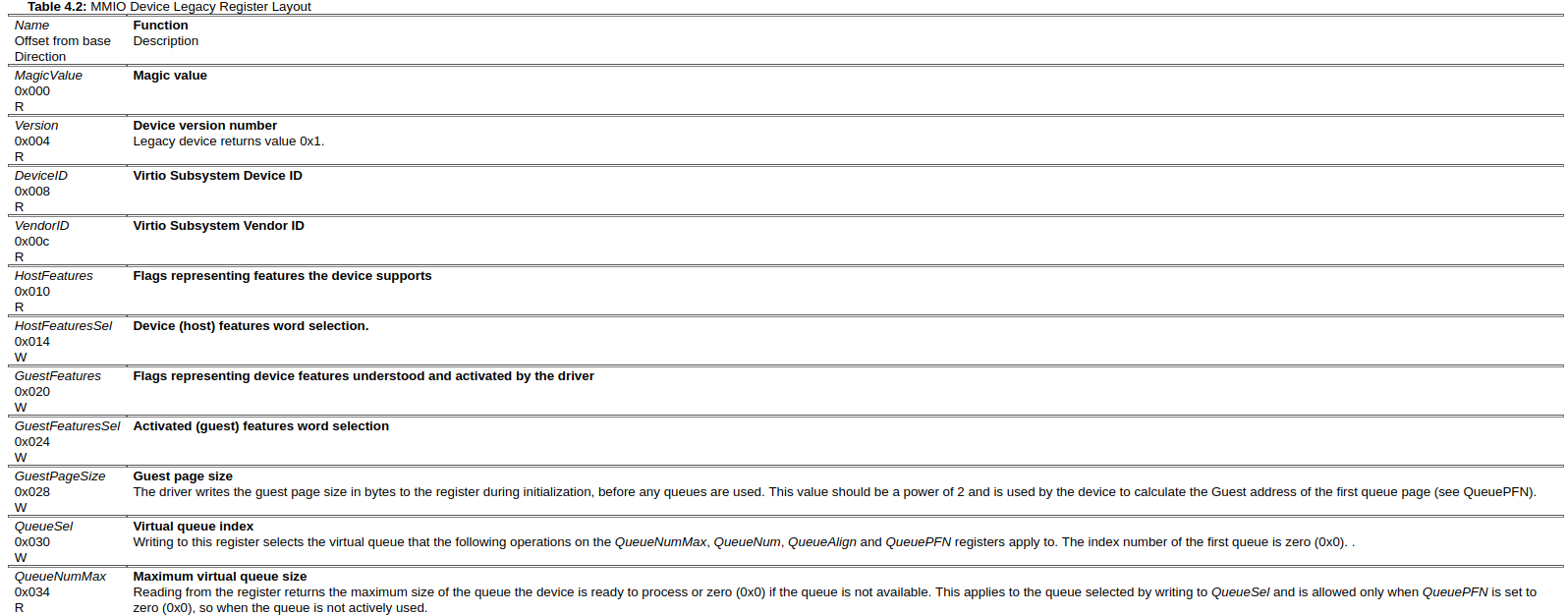

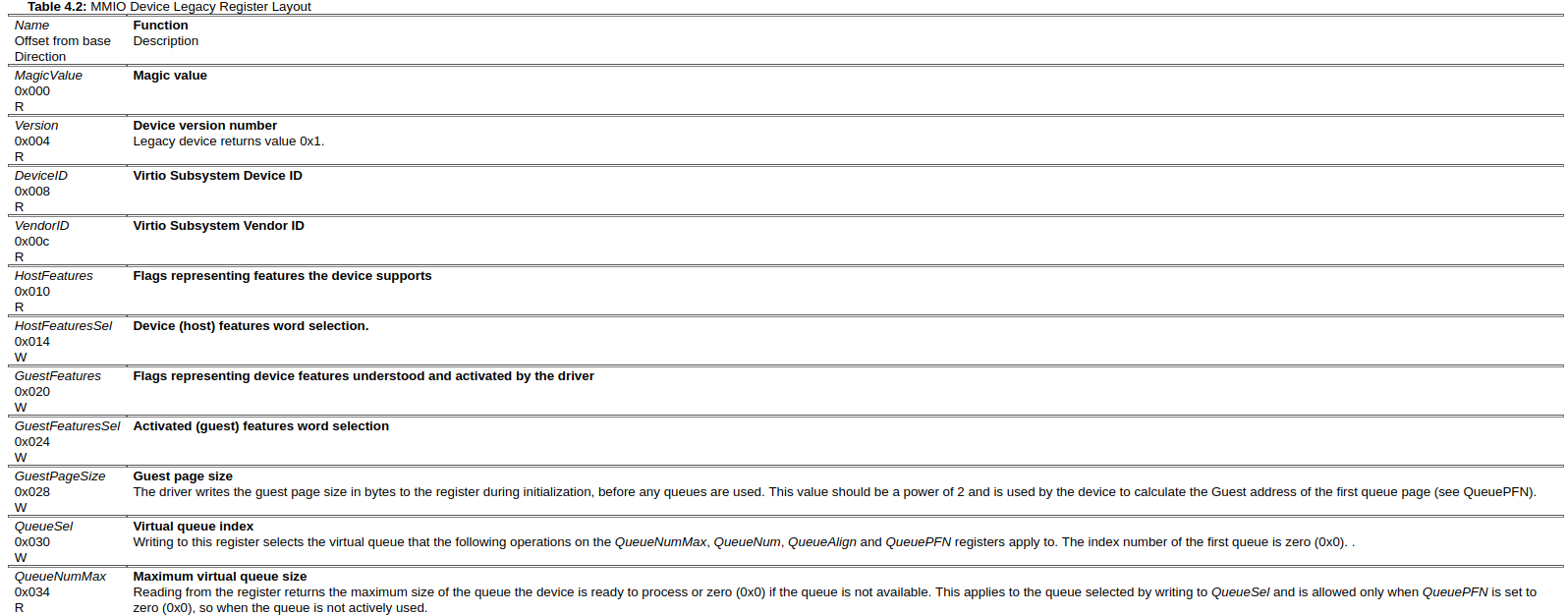

The UART emulated in Qemu is the NS16550A UART chipset. We control the UART using MMIO programming. The Base address of the UARTs begins at 0x1000_0000 and each UART device is given an offset of 0x100 (256 bytes)

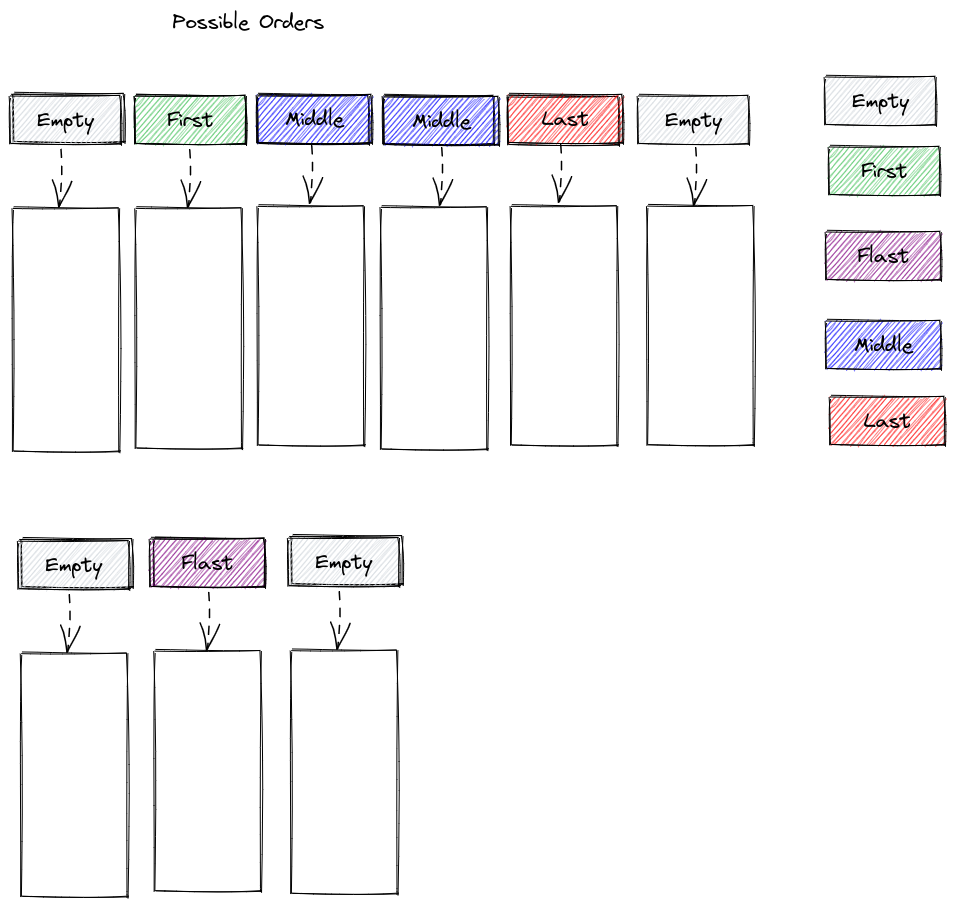

The UART has 8 physical registers that can be interpreted as 12 logical registers... this is because some of the physical registers can be used differently under different contexts. For example The Buffer Register can be used as an input register when the UART is idle, but when the UART is not idle, the same register will be treated as an output register.

Below is a diagramatic representation of the UART registers :

Notice that there are registers that share the same physical space. For exapmple.... see below

From the image, there are only 8 bytes of spaces used to represent all the 12 registers. This is becuse there are registers that share byte space :

- The Receive Buffer Register(RBR), The Transmitter Holding Register(THR) and the Divisor Latch Least Significant Byte (DLL) can occupy the same byte space.

- The interrupt Status Register and the FIFO control Register occupy the same byte space.

- The Line Status Register and the Prescaler Division can occupy the same byte space.

- The Interrupt Enable Register and the Divisor Latch Most significant Byte share the same byte space.

All registers are 8 bits long. We will not discuss the DLL, DLM and PSD registers.

1. The Line Control Register

The line control Register is used to configure the UART communications.

Using this register, you can set the format of the data frames being transported.

Using this register, you can set the size of the data frame.

Using this register, you can determine whether we will be able to set a custom baud rate or use the default baud rate.

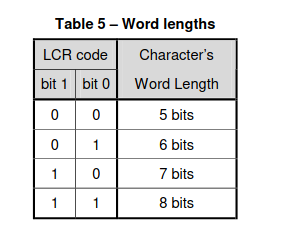

- Bits [1:0] are used to set the word_length ie. the length of the Data frame. The legal values are :

- Bit [2] is used to set the number of stop bits to be included in the transmission frame : 0==one stop_bit and 1 == two stop bits

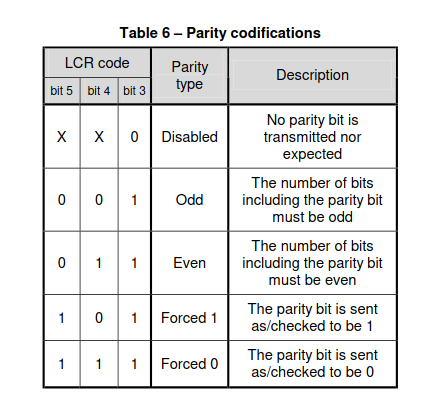

- Bits [5-3] are used to set the parity type of the data frame to be transmitted

- Bit[7] is the DLAB bit. Setting this to 1 means that we get to acces the DLL, DLM and PSD registers to set the baud rate

2. The Line Status Register

This register contains the info about the communicatiuon line. Also, if any error occurs, it is reflected in this register:

The Buffer register

This register stores data that either has to be transmitted across the communication line OR it has been received from the communication line

When you read from this buffer, it is treated as The Receiver Holding Register

When you write to this buffer, it is treated as The Transmitter Holding Register

3.1 The Receiver Holding Register

This register is used as a data buffer ONLY IF the DLAB bit in the The Line Control Register is set to zero.

It acts as a data buffer for the data that has been received from a sender.

It is good practice to confirm that the data is read-worthy before reading it, you might read garbage. To confirm that data is read-worthy, check if the "Data Ready" bit in the status register is set to 1.

3.2 The Transmitter Holding Register

This register stores data that is to be transmitted across the line.

It is good practice to write to this Register ONLY when the buffer is empty. To check if the buffer is empty, check if the "THR Empty" bit in the Linestatus Register is set to 1.

The Interrupt Enable Register

[undone] Explain the Interrup Enable Register

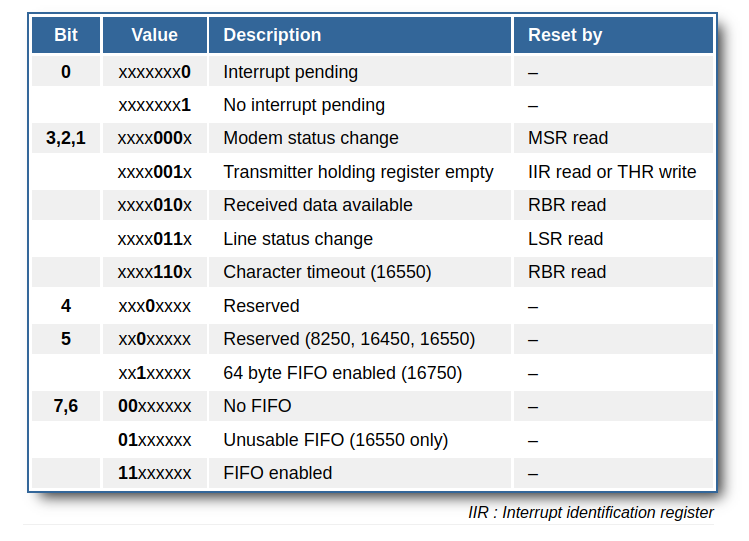

The Interrupt Status Register

This register shows the following info :

[undone] (describe the rest of the registers when you get the time)

- Added and Important

- When Keyboard keys are pressed, they are stored in the UART FIFO_receive_buffer first.

- When the UART realizes that there is new data in the buffer, it does two things :

- It sends a data ready interrupt to the plic.

- It changes the "data ready" bit in the Line status register from zero to one.

- The plic informs the CPU that the UART has new data that needs to be read.

- The CPU traps, it calls the trap handler to check things out

- The trap handler does the following

- Summons the UART driver

- Uses the UART driver to read data from the UART buffer

- Stores the read data in an stdin vector

- Informs the PLIC that the data has been sorted

- PLIC acknowledges that the interrupt has been sorted

- Interrupt handler returns control to the kernel.

- Once the Data has been read, the UART turns off the "Data Ready Bit" in the line status register. It also disables the Interrupt status

- The

- The CPU reads the contents of the FIFO buffer byte by byte. If it reads a single byte, it stores it in the RHR buffer.

More About the UART

You need to configure the UART devices on both the receiver and sender.

Configuration :

- Set the baudrate : communicating devices need to be within 10% range of difference

- Are we going to include the parity bit in our transmissions?

- How are the Interrupts handled?

Configuring the Baud rate:

The Baud Rate formula is as follows :

Divisor = UART_device_clock_frequency / ( Baud_rate x Prescaler_Division_value)

where :

- Divisor is a 16 bit value whose first 8 bits get stored in the DLM register and last 8 bits get stored in the DLL register. If we do not set the DLL and DLM bit, the Divisor value is assumed to be 65,536 (2^16).

- UART_device_clock_frequency is the clock speed of the particular UART implementation. eg 16MHz

- The Baud_rate is the rate at which data transfers, this is what we are trying to calulate.

- The Prescaler_Division_value is found in the Prescaler_Division register. It is represented using 4 bits, its value ranges from 1 to 16. If we do not set the prescaler division value, 16 is assumed to be the default. We are okay with 16

We will use this registers to :

- Initialize the communication between the 2 devices

- fetch and write data to the communication buffers

Now, there is a conflict, The DLL bit occupies the same space that the THR and RHR occupy.

This problem is solved by doing the baud rate configuration once. After that the space is left for RHR and THR.

That space is only usable for the DLL only if the DLAB bit is set to one. When the DLAB bit is set to 1, the UART realized that it is configuration time and dedicates the register to store the DLL bit before it does the bitrate calculation.

So the DLAB bit acts as a switch : When the DLAB bit = 1 then...

- register 000 stores the DLL value

- register 000 stores the DLM value

- register 101 stores the Prescaler value

Once the baud rate configuration is complete, the DLAB bit is set to 0, and the register space that was used for DLL and DLM becomes available for accessing the THR and RHR, respectively. The UART controller switches back to data transmission/reception mode.

Parity Bit

No we do not care about this. It is important, but we are in a virtual environment, why would bits get lost in transmission? We are in a perfect world.

Interrupt handling

THe UART is conected to the CPU via the PLIC. The UART send out 5 kinds of interrupts to the CPU.

-

Receiver Data Available Interrupt (RDA): This interrupt is triggered when data is received and available in the receiver buffer (RBR/RHR) to be read by the CPU.

-

Transmitter Holding Register Empty Interrupt (THRE): This interrupt is triggered when the transmitter buffer (THR) is empty and ready to accept new data to be transmitted.

-

Receiver Line Status Interrupt (RLS): This interrupt is triggered when a line status error occurs during data reception, such as framing errors, parity errors, or overrun errors.

-

Modem Status Interrupt (MS): This interrupt is triggered when there are changes in the modem status signals, such as changes in the CTS (Clear To Send) or DSR (Data Set Ready) signals.

-

Receiver Time-Out Interrupt (RTO): This interrupt is triggered when the receiver is idle for a specified duration, indicating the end of a data transmission.

In our case, We only care about the first 2 interrupts.

To enable the UART device to be able to send interrupts to the CPU, we have to tweak the bits of the Interrupt enable register.

Programming_the_UART

Initializing the Communication between the 2 devices.

Initializing the communications between the 2 devices means that we configure the UART protocol.

We need to define :

- The maximum amount of bits that can be contained in the buffer at a time. The 2 devices need to agree on this so that data does not get lost if one of the devices buffer is too small.

- Set the order of reading and writing to the communication buffer. In our case, we set the order to FIFO (First in First Out).

- Define how the CPU and the UART will communicate with each other when the buffer is ready to be read or written to. You can choose between 2 methods ; Poll driven communication od Interrupt driven communication.

In Interrupt driven communication, the UART device sends interrupt signals to the CPU whenever the read buffer is full. And consequently, the CPU invokes the appropriate interrupt handler. You have the option to involve the PLIC or not.

In the Poll driven communication, the CPU will occasionally check if the buffer is ready to be read or written to. - Set the data transfer speed between the 2 devices - the baud rate. This is to avoid data loss.

But here is a relief : If we set the DLAB (Divisor Latch access bit) to zero, then :

- The Prescaler Division Register becomes inaccessible. Meaning that the Line status register does not have to share the byte space.

- The DLL register becomes inaccessible, meaning the RHR and THR don't have to share the byte space.

- The DLM register becomes inaccessible, meaning that the Interrupt Enable Register does not have to share the byte space.

That is the path we will take, we will set the DLAB bit to zero so that we access the registers in a more simple manner. The reason that makes it okay to disregard setting the DLL, DLM and PDS registers is because we do not need them. These three registers are used to set the Baud Rate of the UART device.

We are in Qemu, this is a virtual space. This means that we are not dealing with real physical devices. Because of this fact, it is not necessary to set the Baud Rate. The machine emulates the maximum baud rate available.

The Baud Rate formula is as follows :

Divisor = UART_device_clock_frequency / ( Baud_rate x Prescaler_Division_value)

where :

- Divisor is a 16 bit value whose first 8 bits get stored in the DLM register and last 8 bits get stored in the DLL register. If we do not set the DLL and DLM bit, the Divisor value is assumed to be 65,536 (2^16).

- UART_device_clock_frequency is the clock speed of the particular UART implementation. eg 16MHz

- The Baud_rate is the rate at which data transfers, this is what we are trying to calulate.

- The Prescaler_Division_value is found in the Prescaler_Division register. It is represented using 4 bits, its value ranges from 1 to 16. If we do not set the prescaler division value, 16 is assumed to be the default. We are okay with 16

We will use this registers to :

- Initialize the communication between the 2 devices

- fetch and write data to the communication buffers

Pseudocode for initializing the UART communication

input : the UART base address (hopefully from a struct abstract) output : No_output

- set the word length to 8 bits

- access the lCR register

- set bits [1:0] to [1:1]

- Enable FIFO reads and writes

- access the FIcaler Division RegisFO control Register

- turn the FIFO enable bit to 1

- Set the interrupt capability

- Access the Interupt enable Register

- enable the data ready interrupt [set bit 0 to the value 1]

- enable the transmitter empty interrupt [set bit 1 to the value 1]

- Set the Baud rate

- since we are setting the BAUD rate at 2400, the divisor value is 592

- use bitmasking to separate the most sigificant bytes from the least significant bytes

- Set the DLAB bit to 1 in order to allow setting the Baud rate

- store the two seperate values in the DLL and DLM respectively

Reading from the UART

When the buffer is full, the UART sends an interrupt to the PLIC. The PLIC calls the interrupt handler. The Interrupt handler invokes a UART read (This function that we are writing now). The read input can be directly displayed in the console output or stored in a buffer

Pseudocode

input : the UART base address (hopefully from a struct abstract) output : Option<None, BYTE>

- Access the Line Status Register

- Access the data_ready status bit.

- If the data Bit is 1, continue to step 5

- If the data bit is 0, return None

- Read the RHR buffer and return the read byte.

When the interrupt handler calles read function, it stores the inputs in a curcular buffer. From this buffer you can choose hich inputs to display to the console or process

Control flow diagram of the UART read

graph TD

A[ Access the Line Status Register] --> B[Access the data_ready status bit];

B --> C{Is the Data Ready?} ;

C --> |Yes| D[Read the RHR buffer];

D --> E[return the read byte];

C --> |No| E[return None type]

Writing the UART

When the buffer is empty, the UART sends an interrupt to the PLIC. The PLIC calls the interrupt handler. The Interrupt handler checks if the UART_console_write_buffer is empty. If the Buffer is empty, the Interrupt handler does not call the UART_write function. If the UART_console_write_buffer is not empty, the interrupt handler calls the console_output_feeder.

Pseudocode

input : the UART base address (hopefully from a struct abstract), the byte to be written output : Result<Ok, Err>

- Access the Line Status Register

- Confirm that the THR is empty

- If the data Bit is 1, continue to step 5

- If the data bit is 0, return Err

- Write to the THR buffer and return an OK().

When the interrupt handler calles read function, it stores the inputs in a curcular buffer. From this buffer you can choose hich inputs to display to the console or process

Control flow diagram of the UART read

graph TD

A[ Access the Line Status Register] --> B[Access the THR_Empty status bit];

B --> C{Is the THR Empty?} ;

C --> |Yes| D[Write to the THR buffer];

D --> E[return an OK];

C --> |No| F[return Err]

UART Buffer management

Data coming from the keyboard can either be displayed to the console or stored for further processing. For this reason we will have a ring buffer for storing read input. Whatever you choose to do with this data is up to you

With this input buffer, we can implement scanf. We can also confortably implement a function that continuously reacts keyboard input. (eg, continuous console display)

Data coming from the programs might also need to be displayed . That is why we have the UART_console_write_buffer. Strings from the user or kernel programs get stored in this queue. From there, when we receive a THR_empty interrupt,

Driver exposed API

- Clear input buffer (everyone)

- Read input buffer (everyone)

- Read line (Everyone)

- Read word (Everyone)

- Write word (Everyone)

- Write line (Everyone)

- Determine interrupt type (User PLIC)

Interaction with the PLIC

The PLIC receives interrupts from the UART whenever the Data Buffer is full_and_ready_to_be_read. When the PLIC receives this interrupt, it does not really know what the interrupt is all about. So it needs to read in the UART Line Status Register and determine which event caused the interrupt. This situation is valid only when the UART is set to send interrupts because of many reasons.

However in our case, the PLIC sends interrupts only when Data Buffer is full_and_ready_to_be_read, so we do not need a function to determine the type of interrupt. the type of interrupt is always "data Ready"

Principles when abstracting hardware

- The struct used to abstract the hardware MMIO map should be compiled in a predictable manner (C ABI)

- We should always use volatile reads and writes to the MMIO registers

- In software, we should be able to share any number of read-only accesses to these peripherals

- If some software should have read-write access to a peripheral, it should hold the only reference to that peripheral

Why use the C ABI?

The C ABI is used for the sake of compatibility and predictability. For example, the Rust struct fields can get re-ordered while the C structs field order is static. For example, if a struct field has 2 integer fields and 1 boolean, normally the field order would be as declared. But if the boolean is accessed more frequently, it might be re-odered and placed at the beginning to improve cache locality.

In this case, we need the struct order as static.

Why use volatile reads and writes?

When you write to the same memory address for a couple of times, the compiler might optimize the code and just consider the last write value. Meaning you will lose a couple of writes due to compiler optimization.

When you read from the same memory a couple of times, the compiler might optimize the reads using a cache; Volatile read the image, there are onl

Why we won't use global mutable variables to abstract our UART driver